- Автоматизация

- Антропология

- Археология

- Архитектура

- Биология

- Ботаника

- Бухгалтерия

- Военная наука

- Генетика

- География

- Геология

- Демография

- Деревообработка

- Журналистика

- Зоология

- Изобретательство

- Информатика

- Искусство

- История

- Кинематография

- Компьютеризация

- Косметика

- Кулинария

- Культура

- Лексикология

- Лингвистика

- Литература

- Логика

- Маркетинг

- Математика

- Материаловедение

- Медицина

- Менеджмент

- Металлургия

- Метрология

- Механика

- Музыка

- Науковедение

- Образование

- Охрана Труда

- Педагогика

- Полиграфия

- Политология

- Право

- Предпринимательство

- Приборостроение

- Программирование

- Производство

- Промышленность

- Психология

- Радиосвязь

- Религия

- Риторика

- Социология

- Спорт

- Стандартизация

- Статистика

- Строительство

- Технологии

- Торговля

- Транспорт

- Фармакология

- Физика

- Физиология

- Философия

- Финансы

- Химия

- Хозяйство

- Черчение

- Экология

- Экономика

- Электроника

- Электротехника

- Энергетика

Сведения об авторах 6 страница

Рис. 8.14. Коммутационный узел «4 х 4»

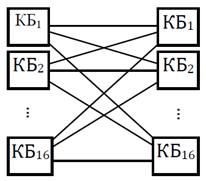

Коммутационный блок (КБ) представляет собой аналогичную КУ структуру, «атомарными» в которой являются КУ (рис. 8.15).

Рис. 8.15. Коммутационный блок «16 х 16»

Коммутационная сеть по типу Butterfly изображена на рис. 8.16.

Рис. 8.16. Коммутационная сеть по типу Butterfly «256 х 256»

Рис. 8.16. Коммутационная сеть по типу Butterfly «256 х 256»

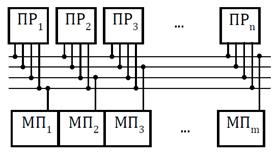

В МВС с общей памятью в качестве средства передачи информации часто используют шины. Каждый модуль памяти имеет свою шину, к которой подключаются все процессорные узлы. Схематически это показано на рис. 8.17.

Рис. 8.17. МВС с общей памятью

Организация схем коммутации в МВС с распределенной памятью

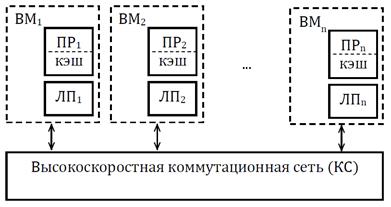

На рис. 8.18 представлена типовая архитектура МВС с распределенной памятью.

Рис. 8.18. Типовая архитектура схем коммутации в МВС с распределенной памятью

При обсуждении этого типа архитектур будем использовать следующие обозначения: число шин – m, число процессоров – n. Также будем учитывать ограничение m n/2. Средства коммутации для этого типа архитектуры представляют важнейший структурный элемент ВС.

Наиболее распространенные решения при построении КС для МВС с распределенной памятью можно разбить на три группы.

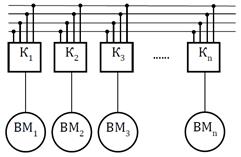

1. ВС со связями через общую шину (см. рис. 8.19).

Такая схема является, с одной стороны, дешевой и просто реализуемой, а также соответствует структуре передачи данных при решении многих вычислительных задач. Легко наращивается число подключаемых вычислительных модулей (ВМ). С другой стороны, для обеспечения эффективной работы шины требуется тщательное планирование использования шины (арбитр шины), работающей в режиме разделения времени, от которой зависит производительность всей системы.

Рис. 8.19. Архитектура схем коммутации в МВС с распределенной памятью со связями через общую шину

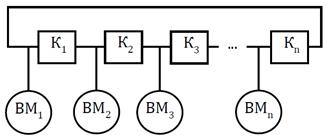

2. Более дорогой вариант – архитектура со связями через несколько шин – представлена на рис. 8.20. При таком способе связи поддерживается режим прямого доступа к памяти, причем передача производится обычно блоками из фиксированного набора слов.

Рис. 8.20. Архитектура схем коммутации в МВС с распределенной памятью со связями через несколько шин

Достоинством архитектур МВС, использующих при коммутации несколько шин, является бо'льшая производительность и надежность, чем у аналогов с одной шиной. Однако для организации эффективных вычислений необходимы n коммутаторов шин, а это высокие аппаратные затраты.

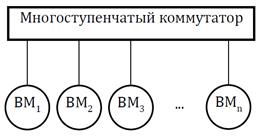

3. На рис. 8.21 представлена архитектура со связями через многоступенчатый переключатель.

Рис. 8.21. МВС с распределенной памятью со связями через многоступенчатый переключатель

Существует большое разнообразие в организации коммутации такого вида.

При соединении первого и последнего процессоров линейки через коммутатор получается топология, называемая кольцом(рис. 8.22).

Рис. 8.22. Многоступенчатый коммутатор кольцевого типа

Система, в которой каждый ВМ связан с каждым другим ВМ прямой линией связи, построена на основе КС с полным набором связей(рис. 8.23). Такая топология обеспечивает высокую надежность и минимальные затраты при передаче данных, однако является сложно реализуемой при большом количестве процессов. Каждый узел – это ВМ со своим многовходовым коммутатором.

Рис. 8.23. Схема КС с полным набором связей

Система, в которой все ВМ с помощью своих коммутаторов имеют линии связи с некоторым центральным коммутатором или центральным коммутационным узлом (ЦКУ) или управляющим процессором, называется ВС с топологией типа «звезда».

Рис. 8.24. Коммутатор по типу «звезды»

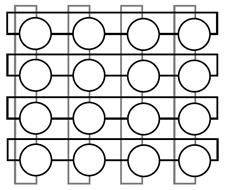

ВС, в которой топология линий связи образует прямоугольную сетку (обычно двух- или трехмерную), называется системой с топологией решетки. Подобная топология может быть достаточно просто реализована и, кроме того, эффективно использована при параллельном выполнении многих численных алгоритмов (например, при реализации методов анализа математических моделей, описываемых дифференциальными уравнениями в частных производных). На рис. 8.25 представлена топология связей по типу «двумерной решетки». Каждый ВМ связан с 4-мя соседями и через них с любыми другими ВМ.

Рис. 8.25. Структура ВС по типу «решетки»

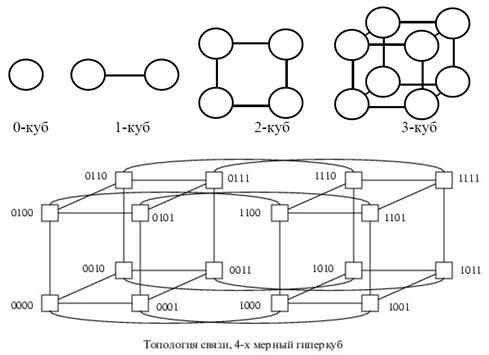

Топология ВС по типу «гиперкуб»– частный случай решетки, когда по каждой размерности сетки имеется только два процессора. Примеры гиперкуб- коммутаторов представлены на рис. 8.26. Гиперкуб содержит 2N процессоров при размерности гиперкуба N.

Рис. 8.26. Коммутатор по типу «гиперкуба»

Такой вариант организации сети передачи данных достаточно широко распространен на практике, достаточно прост в построении, и характеризуется следующими свойствами:

1. Два процессора имеют соединение, если двоичные представления их номеров имеют только одну различающуюся позицию.

2. В N-мерном гиперкубе каждый процессор связан ровно с N соседями.

3. Кратчайший путь между двумя любыми процессорами имеет длину, совпадающую с количеством различающихся битовых значений в номерах процессов. Отсюда следует, что максимальная длина пути в N-мерном гиперкубе равна N.

4. N-мерный гиперкуб может быть разделен на два (N–1)-мерных гиперкуба (всего возможно N таких разбиений).

Очевидные преимущества такой топологии:

1. ВМ, располагаясь в вершине N куба, не отстоит более чем на N-ребер ни от какого другого ВМ, что значительно облегчает создание эффективных коммуникаций в системе (например, для N=12 допустимое число ВМ

212 =4096!);

2. Т.к. структура соединений в N-кубе хорошо согласуется с двоичной логикой, то достаточно легко реализуется алгоритм маршрутизации для передачи сообщений между узлами;

3. Между любой парой ВМ существует несколько альтернативных путей коммуникаций, что позволяет в целом снизить задержки при передачах.

Архитектура систем со смешанной организацией памяти

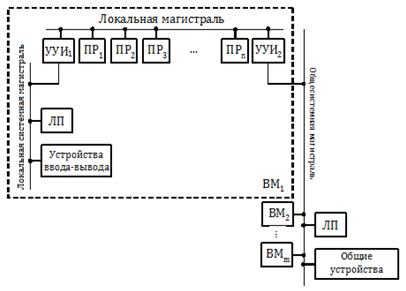

Для решения практических задач часто используют вычислительные системы со смешанной организацией памяти. На рис. 8.27 схематично представлен пример такой архитектуры.

Рис. 8.27. Типовая архитектура систем со смешанной организацией памяти Здесь: УУИ1, УУИ2 – устройства управления интерфейсами; ПР – процессор; ЛП – локальная память; ВМ – вычислительный модуль.

Литература

1. Современные операционные системы : Пер. с англ. / Э. Таненбаум. — СПб.: Питер, 2006. — 1038 с.

2. Сетевые операционные системы : Учебник для вузов / В. Г. Олифер, Н. А. Олифер. — СПб.: Питер, 2009. — 668 с.

3. Основы современных операционных систем : Учеб. пособие для вузов / В. О. Сафонов. — М.: ИНТУИТ, 2011. — 583 с.

4. Архитектура ЭВМ и систем : учебное пособие для бакалавров / О. П. Новожилов. — М.: Юрайт, 2015. — 528 с.

5. Архитектура ЭВМ и операционные среды : Учебник для вузов / В. Г. Баула, А. Н. Томилин, Д. Ю. Волканов. — М.: Академия, 2012. — 336 с.

6. Организация ЭВМ и систем : Учебник для вузов / С.А.Орлов, Б.Я. Цилькер — СПб.: Питер, 2015. — 668 с.

Сведения об авторах

Мусихин Александр Григорьевич, кандидат технических наук, доцент кафедры вычислительной техники института информационных технологий Российского технологического университета – МИРЭА.

Смирнов Николай Алексеевич, кандидат технических наук, доцент, профессор кафедры вычислительной техники института информационных технологий Российского технологического университета – МИРЭА.

|

|

|

© helpiks.su При использовании или копировании материалов прямая ссылка на сайт обязательна.

|