- Автоматизация

- Антропология

- Археология

- Архитектура

- Биология

- Ботаника

- Бухгалтерия

- Военная наука

- Генетика

- География

- Геология

- Демография

- Деревообработка

- Журналистика

- Зоология

- Изобретательство

- Информатика

- Искусство

- История

- Кинематография

- Компьютеризация

- Косметика

- Кулинария

- Культура

- Лексикология

- Лингвистика

- Литература

- Логика

- Маркетинг

- Математика

- Материаловедение

- Медицина

- Менеджмент

- Металлургия

- Метрология

- Механика

- Музыка

- Науковедение

- Образование

- Охрана Труда

- Педагогика

- Полиграфия

- Политология

- Право

- Предпринимательство

- Приборостроение

- Программирование

- Производство

- Промышленность

- Психология

- Радиосвязь

- Религия

- Риторика

- Социология

- Спорт

- Стандартизация

- Статистика

- Строительство

- Технологии

- Торговля

- Транспорт

- Фармакология

- Физика

- Физиология

- Философия

- Финансы

- Химия

- Хозяйство

- Черчение

- Экология

- Экономика

- Электроника

- Электротехника

- Энергетика

Сведения об авторах 2 страница

Прежде всего, вспомним сведения, известные из курса информатики.

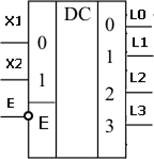

Дешифратор

Это устройство, которое имеет единицу только на одном из выходов, соответствующему коду входных информационных сигналов.

Дешифратор на схемах обозначается следующим образом:

Таблица соответствия для двухвходового дешифратора имеет вид:

| Е | Х2 | Х1 | L0 | L1 | L2 | L3 |

| X | X |

Вход Е означает разрешение работы дешифратора. Этот вход обычно делают инверсным. Если разрешение есть, то  =0, и один из выходов в соответствии с кодом входных информационных сигналов дешифратора равен 1. Если E=1, то независимо от состояния входных сигналов все выходы дешифратора равны 0.

=0, и один из выходов в соответствии с кодом входных информационных сигналов дешифратора равен 1. Если E=1, то независимо от состояния входных сигналов все выходы дешифратора равны 0.

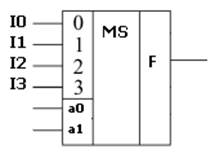

Мультиплексор

Из многих информационных входов I0…I3 мультиплексор подает на выход один, соответствующий коду, установленному на управляющих входах a1, a0. Структурная схема мультиплексора имеет вид:

Таблица соответствия:

| a1 | a0 | F |

| I0 | ||

| I1 | ||

| I2 | ||

| I3 |

Регистр

Регистры обычно строятся на D триггерах. Обозначение регистра на схемах может иметь вид:

На вход С подается синхросигнал. Регистр может срабатывать по переднему или по заднему фронту синхроимпульса. Вход S – управляющий. При S=0 регистр осуществляет хранение информации. При S=1 регистр переписывает свое состояние по синхросигналу в соответствии с состоянием входных информационных сигналов.

Синхросигнал обычно подается в виде импульса. При этом регистр изменяет свое состояние по переднему (возрастающему) или по заднему (спадающему) фронту импульса. В первом случае вход С обозначается с наклонным штрихом слева-снизу направо-вверх, во втором – со штрихом слева-сверху направо-вниз.

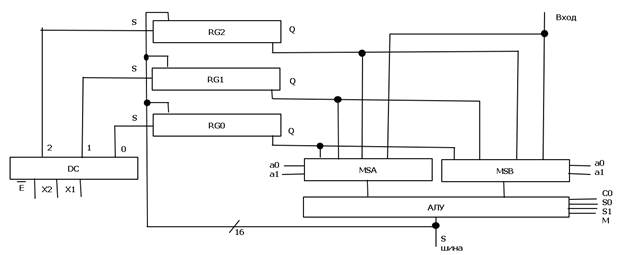

Рассмотрим схему центрального процессора (операционное устройство) в 2 этапа. Сначала рассмотрим упрощенную схему. Затем усложним её.

Рис. 2.3. Схема вспомогательная

Подачей управляющих сигналов на дешифратор, мультиплексоры и АЛУ ведает устройство управления ЦП, которое выдает так называемое управляющее слово процессора. Оно состоит из разрядов управления этими устройствами. – по 2 разряда на мультиплексоры MSA и MSB, 3 разряда на дешифратор DS и 4 разряда на АЛУ.

| MSA | MSB | АЛУ | DC | |||||||||||

| a0 | a1 | a0 | a1 | M | S1 | S0 | C0 | E | X2 | X1 | ||||

Рассмотрим примеры.

1.Пусть надо в RG1 поместить сумму чисел из RG2 и RG0:

RG1 ← RG2 + RG0

2. RG2 ←вход

| ХХ |

3. RG0 ← RG2 ۸ вход

| 110Х |

4. S ← RG1

| ХХ | 1ХХ |

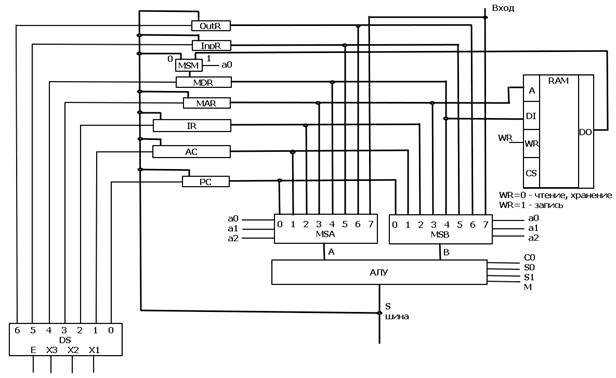

Рассмотрим более полный вариант схемы ЦП.

Рис. 2.4. Схема ОУ ЦП

Управляющее слово ВМ будет составлено из управляющих разрядов MSA, MSB, АЛУ, DS, MSM, WR.

| MSA | MSB | АЛУ | DC | MSM | WR | ||||||||||||||||||

| a0 | a1 | а2 | a0 | a1 | а2 | M | S1 | S0 | C0 | E | X2 | X1 | X0 | a0 | WR | ||||||||

Рассмотрим примеры управляющего слова ЦП для некоторых операций:

AC ←AC + MDR

| MSA | MSB | АЛУ | DC | MSM | WR |

| x |

MAR ← PC

| MSA | MSB | АЛУ | DC | MSM | WR |

| xxx | x |

MDR ← M[MAR]

| MSA | MSB | АЛУ | DC | MSM | WR |

| xxx | xxx | xxxx |

Пустой такт NOP

| MSA | MSB | АЛУ | DC | MSM | WR |

| xxx | xxx | xxxx | 1xxx | x |

Таким образом, мы спроектировали схему операционного устройства центрального процессора учебной ВМ.

2.4. Устройство управления ЦП

Задача устройства управления – обеспечить выдачу управляющего слова ЦП. Иначе он называется микрокод, который управляет работой аппаратуры ЦП. Обычно он записывается в постоянное запоминающее устройство (ПЗУ) центрального процессора (прошивается).

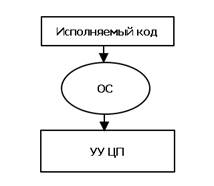

Что должно делать УУ? У нас есть исполняемый код программы. Дальше в ходе выполнения исполняемого кода на ВМ им занимается операционная система – программа, которая выдаёт команды для УУ ЦП.

Рис. 2.5. Алгоритм управления в ВМ

Последовательность работы устройства управления задается циклами.

Для начала рассмотрим цикл выборки команды. Ведь прежде чем выполнить команду, надо выбрать её из памяти ВМ.

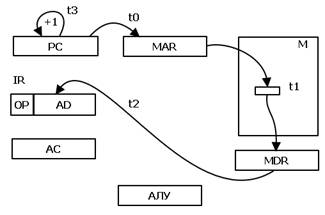

Рис. 2.6. Цикл выборки команды

Для выборки команды из памяти ВМ надо, во-первых, поместить адрес команды из регистра адреса команды в регистр адреса памяти, во-вторых, прочитать команду из ячейки памяти в регистр данных памяти, в-третьих. Переслать команду в регистр команды, в-четвертых, подготовить счетчик команд для выборки следующей команды – инкрементировать PC.

То есть, последовательно надо выполнить 4 действия, обозначенные на рис. 2.6 t0, t1, t2, t3. Следовательно, цикл выборки команды осуществляется за 4 такта.

Само выполнение команды происходит следующим образом:

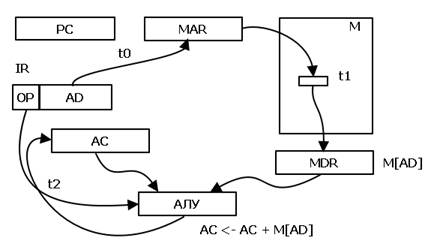

Рис. 2.7. Цикл выполнения команды

Рассмотрим цикл выполнения команды на примере операции сложения.

Нулевой такт – пересылка адреса операнда из регистра команды в регистр адреса памяти. Первый такт – выборка из памяти операнда и размещение его в регистре данных памяти. Второй такт – собственно выполнение сложения в АЛУ с размещением результата в аккумуляторе.

Здесь мы рассматриваем выполнение команды с прямой адресацией, когда в адресном поле команды находится адрес операнда.

Машину Фон Неймана стали совершенствовать, поскольку для выполнения некоторых команд более удобными являются другие методы адресации операндов. Всего способов адресации насчитывается около 20. Из них в каждой конкретной ВМ используется только часть, по выбору конструкторов ВМ и в соответствии с назначением ВМ (ориентированием ВМ на обработку определённых видов информации).

Допустим, что у нас в памяти содержится такая информация:

| Адрес | Содержание |

Рассмотрим выполнение команды LDA (загрузку аккумулятора) с помощью различных методов адресации.

Прямая адресация: LDA 30 /загрузить в аккумулятор слово из ячейки с адресом 30. В результате выполнения команды АC ← 40.

Непосредственная адресация: LDA # 30. /загрузить в аккумулятор слово «30». В результате выполнения команды АC ← 30. То есть в команде содержится сам операнд, и загрузка его из памяти не требуется.

Косвенная адресация: LDA @ 30. /загрузить в аккумулятор слово из ячейки, адрес которой находится в ячейке 30. В результате выполнения команды АC ← 50. То есть в команде содержится не адрес операнда, а адрес адреса операнда. Соответственно, для подготовки операции требуется двойное обращение к памяти.

Существуют и другие способы адресации, которые здесь мы не будем рассматривать.

В общем случае для указания способа адресации в команде выделяется отдельное поле, содержащее необходимое количество разрядов. Для декодирования способа адресации при этом необходим ещё один цикл – цикл дешифрации команды.

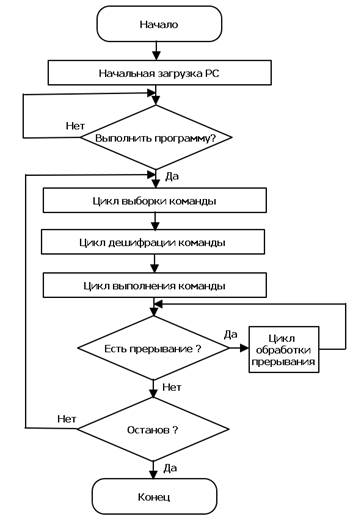

Таким образом, мы получили наличие в УУ ЦП следующих циклов:

1) Цикл выборки команды – С0;

2) Цикл дешифрации команды – С1;

3) Цикл выполнения команды – С2;

4) Цикл обработки прерывания – С3.

Рис. 2.8. Алгоритм работы устройства управления ЦП ВМ

Последний цикл необходим для обработки требований прерывания, вырабатываемых внешними устройствами ВМ (например, клавиатурой, устройством ввода/вывода и т.д.) или при появлении нештатных ситуаций при выполнении команд (деление на ноль, переполнение разрядов и др.). Как происходит цикл обработки прерывания мы рассмотрим позднее – при изучении операционных систем.

На основании изложенного алгоритм работы УУ ЦП имеет вид, представленный на рис. 2.8.

Как видите, ВМ реагирует на прерывание только после окончания выполнения очередной команды программы. В противном случае очень трудно запомнить текущее состояние ЦП для возврата в программу после обработки прерывания.

2.5. Структурная схема УУ ЦП

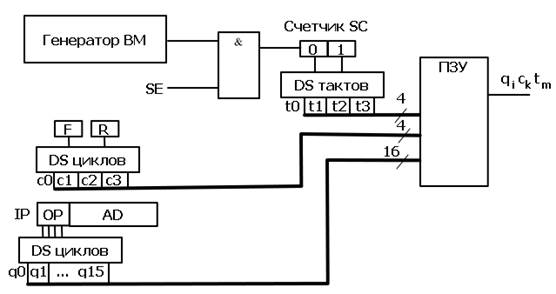

Структурная схема УУ ЦП изображена на рис. 2.9.

В основе УУ имеется ПЗУ; сигналы, вырабатываемые на его выходе, управляют работой ВМ. Генератор ВМ вырабатывает тактовую частоту. Сигнал SE представляет собой сигнал разрешения работы и останов. При SE=0 сигналы генератора ВМ не проходят через схему совпадения, и схема управления не работает – останов. При SE=1 сигналы генератора ВМ проходят через схему совпадения и поступают на вход двухразрядного счетчика, соединённого по выходу с дешифратором тактов. Логика работы последнего приведена на рис. 2.10.

Рис. 2.9. Структурная схема УУ ЦП

| ГИ | ||||||||||||||||||

| t0 | ||||||||||||||||||

| t1 | ||||||||||||||||||

| t2 | ||||||||||||||||||

| t3 | ||||||||||||||||||

Рис. 2.10. Временная диаграмма работы DS тактов

В ВМ такты не пересекаются по времени.

DS циклов работает по выходам двух триггеров F и R. В зависимости от состояния этих триггеров формируется сигнал на соответствующем его выходе.

| F | R | Цикл | Обозначение цикла |

| Выборки команды | С0 | ||

| Дешифрации команды | С1 | ||

| Выполнения команды | С2 | ||

| Прерывания | С3 |

DS команды работает по состоянию разрядов регистра команд, соответствующих полю кода операции. В нашем случае код имеет 4 разряда, что соответствует 16 выходам дешифратора команд.

Выходы всех трех дешифраторов составляют адрес ПЗУ, в котором записана (прошита) информация соответствующая содержимому управляющего слова процессора данного такта данного цикла данной команды.

Такова в общем виде структура УУ ЦП.

Таблица команд учебной ВМ представлена в табл.2.1.

Обычно ВМ содержит команды различной длины – безадресные, одноадресные, двухадресные и др. В нашей учебной ВМ мы рассматриваем все команды единой длины равной 16 двоичным разрядам. Поэтому безадресные команды (с номерами от 12 до 15) содержат фиктивный адрес, равный FFF.

Рассмотрим для примера команду сложения ADD. Для неё в поле кода операции будет иметься значение 2 16-ричного кода. В адресном поле находится 12-разрядный адрес AD. Напишем микрокоманды циклов выборки и выполнения команды.

F=0, R=0, С0=1

С0t0 : MAR← PC / подготовить выборку команды из памяти.

С0t1 : MDR← M[MAR] / прочесть команду из памяти по адресу MAR.

С0t2 : IR← MDR / поместить команду в регистр команды.

С0t3 : PC← PC +1, F← 1/ подготовить адрес след. команды, перейти к циклу выполнения команды.

F=1, R=0, С2=1

С2t0 : MAR← IR[AD] / передать адрес операнда в регистр адреса памяти MAR.

С2t1 : MDR← M[MAR] / прочесть операнд из памяти по адресу MAR.

С2t2 : AC← AC+MDR / выполнить сложение.

С2t3 : F← 0/ перейти к циклу выборки команды.

Так выполняются микрокоманды ВМ в циклах выборки и выполнения команды сложения. Аналогичным образом можно описать порядок выполнения любой команды из перечня команд ВМ.

ВМ фон Неймана первоначально была рассчитана, как и наша учебная ВМ, только для одного типа адресации – прямой адресации. Для других типов адресации, что задаётся обычно в специальном поле команды, требуется наличие цикла дешифрации команды и осуществление выборки операндов соответствующим образом. Мы цикл дешифрации команды не рассматриваем, поскольку считаем, что используется только прямая адресация операндов.

Следующая контрольная работа состоит в том, чтобы вы научились строить команды из микрокоманд подобно рассмотренному примеру. Объем работы в контрольной работе велик. Для оформления работы надо использовать по крайней мере один лист формата А4.

Рассмотрим типовую задачу и приведём пример её решения.

Задача. По адресу 5А8 записана команда сложения ADD с адресом F12. По этому адресу записан операнд 731F. В регистре АС находится операнд 8721. Определить информацию, которая будет иметься в регистрах ВМ PC, MAR, MDR, IR, AC после выполнения данной команды.

Решение.

1. Определяем исходное состояние регистров.

2. Выписываем микрокоманды циклов выборки команды и выполнения команды.

3. Рассчитываем управляющие слова ВМ для каждой микрокоманды.

4. Определяем значения регистров после выполнения каждой микрокоманды.

5. Результаты оформляем в виде табл.2.2.

Таблица 2.2.

| Управл. сигналы, регистры | MSA | MSB | АЛУ | DS | MSM | WR | FR | PC | MAR | MDR | IR | AC |

| Исх. состояние регистров | 5А8 | |||||||||||

| С0t0 : MAR← PC | xxx | x | 5А8 | |||||||||

| С0t1 : MDR← M[MAR] | xxx | xxx | xxxx | 2F12 | ||||||||

| С0t2 : IR← MDR | xxx | x | 2F12 | |||||||||

| С0t3: PC←PC+1, F←1 | xxx | x | 5А9 | |||||||||

| q2С2t0 : MAR← IR[AD] | xxx | x | F12 | |||||||||

| q2С2t1 : MDR← M[MAR] | xxx | xxx | xxxx | 731F | ||||||||

| q2С2t2 : AC← AC+MDR | x | FA40 | ||||||||||

| q2С2t3 : F← 0 | xxx | xxx | xxxx | 1xxx | x |

Таким образом, мы рассмотрели архитектуру устройства управления и операционного устройства учебной ВМ и принципы ее работы.

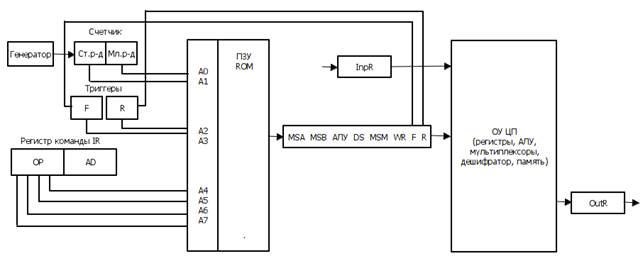

В результате мы получили следующую структурную схему ВМ:

Рис. 2.11. Структурная схема ЦП.

Как видно из схемы, ПЗУ может работать и без дешифраторов на входе, то есть к адресным входам ПЗУ подключены непосредственно выходы счетчика тактов, выходы регистров F, R и выходы поля кода операции регистра команды IR. Благодаря этому адрес ПЗУ состоит из 8 разрядов, и ёмкость ПЗУ существенно уменьшается без потери функциональности.

На выходе ПЗУ имеется управляющее слово ЦП, состоящее из 18 разрядов. Это слово поступает на соответствующие управляющие входы устройств операционного устройства ВМ. На схеме отдельно выделены регистры ввода-вывода, предназначенные для связи ВМ с внешним миром, а также показан регистр команды IR, который входит одновременно в состав УУ и ОУ ЦП ВМ.

3. Архитектура операционных систем

3.1. Терминология

В мире существует множество ВМ. Управляющие слова, непосредственно управляющие устройствами ВМ, называются микрокодом. Микрокод заносится в ПЗУ УУ ВМ. Этот процесс называется прошивкой. Этот термин исторически произошел от того, что ранее существовавшие ПЗУ основывались на ферромагнитных кольцах, характеризуемых хранением информации в зависимости от направления проводов, проходящих через кольца. На заводах по изготовлению ПЗУ были заняты в основном женщины, которые буквально с иглой в руках прошивали каждый бит (кольцо) проводами в заданном направлении. Отсюда и термин «прошивка». С тех пор изменилась элементная база ПЗУ, занесение информации в него производится другими способами, но термин программирования ПЗУ «прошивка» остался.

Следующий термин – опкод (операционный код). Это содержимое регистра команды, включающее код операции и адресную часть.

Таким образом, в архитектуре вычислительной машины выделяются несколько уровней:

1. Уровень цифровой логический – микросхемный, включающий микросхемы И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ, регистры, сумматоры, дешифраторы, мультиплексоры и т.д.

2. Уровень микроархитектуры – это построение ОУ ЦП, УУ ЦП, других крупных узлов процессора.

3. Уровень архитектуры набора команд.

4. Уровень операционной системы.

5. Уровень ассемблера – собственно машинного языка в символьных кодах, построения исполняемого кода с помощью соответствующих системных программ (транслятора, загрузчика, компоновщика и др.)

3.2. Операционная система

Первое, что делает ОС – это выделяет вашей исполняемой команде область в оперативной памяти ВМ. В этой области выделяются участки (сегменты), обладающие разными правами по доступу к ним и предназначенные для разных целей.

| Стек |

| Куча |

| БУП |

| Исполняемый код |

| Данные |

Рис.3.1. Разделы памяти процесса.

В первую очередь – это сегмент данных, поименованных в программе – так называемые глобальные переменные. Во-вторых, это сегмент исполняемого кода, который, как правило, не подлежит изменению в ходе выполнения программы. В-третьих, - это блок управления процессом (дескриптор или РСВ) – основные сведения о процессе. В-четвертых, это стек, используемый для временного хранения данных при прерываниях программы. В-пятых, это так называемая куча, динамическая память процесса, где хранятся все временные переменные и другие данные, используемые в ходе вычислительного процесса.

Приведем пример. Пусть на нашей ВМ надо выполнить программу, вычисляющую формулу F=B+C.

Программа для вычисления в системе команд учебной ВМ выглядит в виде совокупности следующих операций:

LDA B

ADD C

STA F

После компиляции получаем исполнительный код, размещенный в памяти машины, например, с ячейки 010. Пусть данные размещены в памяти, начиная с ячейки 100. Тогда получаем следующее распределение памяти.

| Адрес | Данные | Пояснение |

| Исполняемый код | ||

| … | ||

| B | Данные | |

| С | ||

| F | ||

| … |

3.3. Место операционной системы в ВМ

Место ОС в ВМ поясняется рис.3.2. Нижний уровень А – это уровень аппаратуры. Выше размещена ОС. Еще выше размещается прикладное ПО, т.е. те программы, которые выполняют задачи пользователя.

Рис.3.2. Место ОС в ВМ.

ОС имеет 2 лица: одно обращено к аппаратуре, другое – к нашей программе.

3.4. Задачи ОС

1-я задача ОС – скрыть от пользователя все детали аппаратуры и представить в ВМ в виде определенной рабочей среды – рабочего стола.

2 –я задача ОС (по отношению аппаратуре) – эффективное управление аппаратурой, всеми ресурсами в ВМ.

Какими ресурсами в ВМ мы располагаем? На ВМ работают, а правило, несколько программ одновременно. Каждая из них претендует на использование ресурсов ВМ. Первый ресурс – это время центрального процессора. Второй ресурс – оперативная память. Часто ее не хватает. Поэтому приходится организовывать взаимодействие с дисковой памятью. Третий ресурс – это система ввода-вывода. Ею надо эффективно управлять. Четвертый ресурс – файловая система, обеспечивающая хранение и пользование данными и программами на диске.

Диски в ВМ обозначаются буквами C, D, E … операционная система ка правило, размещается на диске С, и загружается при включении ВМ. Почему диски нумеруются не с буквы А? Раньше буквами А и В обозначались гибкие диски, на диске А размещалась ОС. Современные ОС по объему не вмещаются на гибкий магнитный диск.

3.5. Многослойная структура ОС.

Уровни ОС (слои) обозначаются в виде концентрических колец. (рис.3.3). На рис.3.3 обозначено:

1. Средства аппаратной поддержки.

2. Машинно-зависимые компоненты ОС.

|

|

|

© helpiks.su При использовании или копировании материалов прямая ссылка на сайт обязательна.

|