- Автоматизация

- Антропология

- Археология

- Архитектура

- Биология

- Ботаника

- Бухгалтерия

- Военная наука

- Генетика

- География

- Геология

- Демография

- Деревообработка

- Журналистика

- Зоология

- Изобретательство

- Информатика

- Искусство

- История

- Кинематография

- Компьютеризация

- Косметика

- Кулинария

- Культура

- Лексикология

- Лингвистика

- Литература

- Логика

- Маркетинг

- Математика

- Материаловедение

- Медицина

- Менеджмент

- Металлургия

- Метрология

- Механика

- Музыка

- Науковедение

- Образование

- Охрана Труда

- Педагогика

- Полиграфия

- Политология

- Право

- Предпринимательство

- Приборостроение

- Программирование

- Производство

- Промышленность

- Психология

- Радиосвязь

- Религия

- Риторика

- Социология

- Спорт

- Стандартизация

- Статистика

- Строительство

- Технологии

- Торговля

- Транспорт

- Фармакология

- Физика

- Физиология

- Философия

- Финансы

- Химия

- Хозяйство

- Черчение

- Экология

- Экономика

- Электроника

- Электротехника

- Энергетика

Сведения об авторах 1 страница

Содержание

1. Вычислительный процесс в ЭВМ.. 4

1.1. Команды ЭВМ.. 6

1.2. Формат команды.. 6

1.3. История форматов команд. 7

1.4. Примеры выполнения простой программы на ЭВМ.. 9

2. Архитектура ВМ.. 11

2.1. Логическое проектирование учебной ВМ.. 11

2.2. Центральный процессор. 13

2.3. ОУ ЦП учебной ВМ.. 13

2.4. Устройство управления ЦП.. 19

2.5. Структурная схема УУ ЦП.. 22

3. Архитектура операционных систем. 26

3.1. Терминология. 26

3.2. Операционная система. 27

3.3. Место операционной системы в ВМ.. 28

3.4. Задачи ОС.. 28

3.5. Многослойная структура ОС. 29

3.6. История ОС.. 30

4. Процессы и потоки. 32

4.1. Состояние процесса. 32

4.2. Потоки. 33

5. Управление памятью.. 36

5.1. Страничное распределение. 37

5.2. Сегментное распределение памяти. 40

5.3. Сегментно-страничное распределение памяти. 41

6. Файловая система. 42

6.1. Общие сведения о файлах и файловых системах. 42

6.2. Имена файлов. 43

6.3. Типы файлов. 44

6.4. Организация файла. 46

6.5. Кэширование диска. 51

6.6. Общая модель файловой системы.. 51

6.7. Отображаемые в память файлы.. 54

6.8. Современные архитектуры файловых систем. 56

7. Система прерываний. 58

7.1. Основные понятия. Типы прерываний. 58

7.2. Общая организация прерываний. 59

7.3. Организация системы прерываний с использованием векторов прерываний. 60

7.4. Цикл прерывания. 63

8. Классификация и тенденции развития архитектур современных компьютеров 64

8.1. Классификации ЭВМ и ВС.. 64

8.2. Организация схем коммутации. 76

Литература. 84

1. Вычислительный процесс в ЭВМ

Допустим, вы имеете программу, написанную на языке высокого уровня.

Может ли эта программа сразу выполняться на ЭВМ?

Конечно, не может. Для этого необходимо преобразовать программу из так называемого исходного кода - собственно текста программы на языке высокого уровня (ЯВУ) - в исполняемый код. Этот процесс выполняется обычно в несколько этапов.

На первом этапе работает так называемый транслятор. Он может быть выполнен в двух видах: компилятор или интерпретатор. Интерпретатор обычно осуществляет перевод строк программы на ЯВУ последовательно в ходе выполнения программы. Поэтому появление сообщения об ошибке в программе может произойти в самом конце программы и вся работа ВМ пойдет насмарку.

Компилятор же осуществляет анализ всей программы, выделяет память для программы и требуемых переменных и оптимизирует код программы. Выявление ошибок в программе осуществляется еще до её выполнения. Поэтому компилятор обычно сложнее интерпретатора, но в работе предпочтительнее (работает быстрее на этапе выполнения программы и выявляет ошибки раньше, еще до выполнения программы).

Рис. 1.1. Получение исполняемого кода.

В результате работы компилятора образуется так называемый объектный модуль – код на языке ассемблера. Этот модуль обычно имеет расширение .obj и представляет собой приближенный к машинному языку код. В нем вместо обозначений в двоичном коде используются символьные имена переменных, символьные адреса и символьные обозначения команд. Строится таблица символов.

Затем следуют операции редактирования связей в объектном модуле – работает так называемый линкер, который связывает ваш объектный модуль с другими объектными модулями (используемыми в вашей программе функциями). В результате получается загрузочный модуль, наиболее близкий к выполняемому модулю.

Далее работает загрузчик «loader» который подключает к загрузочному модулю подпрограммы из статической системной библиотеки (имеющие расширение .lib). Эти подпрограммы загрузчик подгружает из библиотеки. Если статическая библиотека подгружается полностью, то программа сильно разбухает в объеме. Поэтому применяют динамическую библиотеку, с подгружением подпрограмм только по мере их необходимости – только то, что будет практически использовать процессор в своей работе в ходе выполнения программы.

Иногда исполняемый код можно обработать и запомнить в формате .exe. С такими исполняемыми файлами следует обращаться очень осторожно, поскольку часто они содержат вредоносный код – вирусы, трояны и т.д., особенно, если эти программы взяты из непроверенных источников в интернете. Так, если вы скачиваете электронную книгу в формате pdf, то это безопасно, а если в формате .exe – опасно.

Часто процессы, выполняемые линкером и лоадером объединяют и обозначают процессом «линкование». Если программа имеет большой объем, то этот процесс может выполняться на ЭВМ довольно длительное время.

ЭВМ работает в двоичных кодах. Все, что относится к составлению программы и преобразованию ее в исполняемый код, относится к программированию. Поэтому мы при рассмотрении дисциплины «Архитектура ВМиС» будем рассматривать только работу в машинных кодах с использованием языка ассемблера для именования переменных и операций.

1.1. Команды ЭВМ

Команды ЭВМ могут быть самые разнообразные. Мы в первую очередь рассмотрим команды с двумя операндами типа сложение и умножение.

Что в общем случае входит в команду? Команда должна указывать:

1) Операцию, подлежащую выполнению;

2) Адреса операндов, над которыми производится операция (именно адреса, а не сами операнды!!!);

3) Адрес, по которому следует записать результат операции (адрес результата);

4) Адрес следующей выполняемой команды.

По сути, команда состоит из двух частей: кода операции и адресной части.

| OP | Адресная часть |

Рис. 1.2. Общий вид команды

1.2. Формат команды

Формат команды – это структура команды, то есть количество и назначение полей команды, а также разрядность каждого поля и команды в целом.

Для команды в процессоре отводится отдельный регистр – IR. По-английски команда – это инструкция. По-русски этот регистр обозначается РК – регистр команды. Таким образом, в ЭВМ имеются два регистра для обращения к памяти – MAR – регистр адреса памяти, MDR – регистр данных памяти и теперь добавляем в ЭВМ еще регистр команд – IR.

Рассмотрим, как изменялись форматы команд при развитии ВМ.

1.3. История форматов команд

Вначале использовались команды, имеющие формат, показанный на рис.1.3. ЭВМ, использующие данный формат команд, назывались четырехадресными, в соответствии с количеством полей в адресной части формата команды.

| OP | AD1 | AD2 | ADR | ADI |

| 4 р-да | 12 р-дов | 12 р-дов | 12 р-дов | 12 р-дов |

Рис.1.3. Формат 4-хадресной команды: OP- код операции, AD1, AD2 = адреса 1-го и 2-го операндов, ADR – адрес результата, ADI – адрес следующей команды.

Рассмотрим некоторую учебную ЭВМ, которая содержит 16 операций и память объемом 4К ячеек. Следовательно, для кодирования операции достаточно 4-х разрядов (24 = 16 команд), а для адресации любой ячейки данной памяти требуется 12 разрядов двоичного кода (4К = 212 = 4096 ячеек памяти).

Таким образом, учитывая, что поле OP содержит 4 разряда, а все 4 адресных поля команды содержат по 12 разрядов, получаем 52 разряда - общую разрядность 4-хадресной команды учебной ЭВМ.

Если учесть, что для формирования одного разряда в регистре требуется один триггер на двух активных элементах, а в первых ЭВМ использовались электровакуумные лампы, потребляющие каждая 50 Вт, то для функционирования только одного регистра команд в 4-хадресной ЭВМ требовалось 5200 Вт (равносильно 5 электроутюгам). Отсюда пришли к выводу, что длинные регистры – это плохо. За счет чего можно уменьшить длину регистра?

Команды в памяти ВМ располагаются, как правило, последовательно друг за другом. Поэтому из состава команды убрали один адрес – адрес следующей команды – и заменили его специальным регистром – счетчиком команд. После выполнения очередной команды к нему автоматически добавляется единица, и он указывает адрес следующей команды. Этот регистр назвали PC – программный счетчик. Затем, при появлении микропроцессоров и появлении первых персональных компьютеров фирмы Intel, аббревиатуру PC стали использовать для обозначения персонального компьютера. Для регистра счетчика команд стали использовать IP (точка инструкции). Соответственно, в русском языке для обозначения данного регистра используют аббревиатуры СК (счетчик команд), САК (счетчик адреса команды) или УК (указатель команды). Вы должны знать, что применительно к регистру адреса команды это одно и то же.

В результате удаления одного адресного поля команда стала трехадресной (рис.1.4) и стала содержать 40 разрядов.

| OP | AD1 | AD2 | ADR |

| 4 р-да | 12 р-дов | 12 р-дов | 12 р-дов |

Рис.1.4. Формат 3-хадресной команды: OP- код операции,

AD1, AD2 = адреса 1-го и 2-го операндов, ADR – адрес результата

Следовательно, регистр стал потреблять меньше электроэнергии, получили экономию в количестве аппаратуры.

В дальнейшем в фирме IBM придумали переход на двухадресные команды. Выяснено, что в 70% случаев результат может заменить один из операндов, поскольку тот более не участвует в вычислениях. Естественно, при этом усложнился компилятор, поскольку в оставшихся 30% случаев необходимо сохранять значение второго операнда для последующих вычислений. Это действие возложили на компилятор, чтобы не изменять программы. В результате команда приобрела вид, показанный на рис.1.5. причем второе адресное поле содержит до операции адрес второго операнда, а после выполнения операции – адрес результата.

| OP | AD1 | AD2, ADR |

| 4 р-да | 12 р-дов | 12 р-дов |

Рис.1.5. Формат 3-хадресной команды: OP- код операции,

AD1, AD2 = адреса 1-го и 2-го операндов, ADR – адрес результата

Итого в регистре команд осталось 28 разрядов. Но аппетит приходит во время еды. Задумались, нельзя ли обойтись только одним адресом операнда? Провели исследования, которые показали, что в большинстве случаев результат предыдущего вычисления используется как операнд следующего вычисления. Поэтому в архитектуру процессора добавили еще один регистр – аккумулятор, который использовался как адрес первого операнда и как адрес результата операции (рис.1.6).

| OP | AD |

| 4 р-да | 12 р-дов |

Рис.1.6. Формат 2-хадресной команды: OP- код операции, AD адрес операнда

При этом команда выполняется по алгоритму:

AC ← AC ʘ M[AD],

где AC – аккумулятор, ʘ - любая операция ВМ, M[AD] – содержимое памяти по адресу AD.

Общее количество разрядов команды уменьшилось до 16.

Наконец, сделали следующий шаг. Придумали совсем безадресные команды. Для этого применили особую структуру памяти – стек. Стек – это такая структура памяти, которая растет вверх и используется сверху по принципу последним пришел – первым вышел. (LIFO – last input first output или FILO - first input last output) (рис.1.7).

| |||

| |||

| PUSH | POP | |

Рис.1.7. Стековая структура

Для обращения со стеком используются специальные команды: PUSH – положить в стек, и POP – взять из стека.

1.4. Примеры выполнения простой программы на ЭВМ

Рассмотрим примеры выполнения простой программы на ЭВМ с различными форматами команд. В качестве примера возьмем вычисление функции

Q=B*C + D*E.

Это выражение содержит две операции умножения и одну операцию сложения.

Предположим, что программа, выполняющая данную функцию, находится в памяти, начиная с адреса 11. Для 4-хадресной ЭВМ данная программа может быть представлена следующей последовательностью команд:

11 MUL B, C, T1, 12 / T1← B*C

12 MUL D, E, T2, 13 / T2← D*E

13 ADD T1, T2, Q, 14/ Q←T1+ = B*C + D*E

Здесь B, C, D, E, Q – адреса ячеек памяти, где хранятся соответствующие числа. T1 и T2 – адреса вспомогательных ячеек памяти.

Для удобства восприятия команд необходимо в тексте программы оставлять комментарии, которые пишутся в строках программы после символа / (слэш). Комментарии могут быть достаточно объемными.

Поскольку последний адрес в команде – адрес следующей выполняемой команды, то в нашем случае, когда команды программы расположены в памяти ЭВМ последовательно, можно обойтись без этого адреса, заменив поле команды регистром счетчика команд, который будет наращивать свое значение на 1 после каждой выполненной команды.

Поэтому, исключив последнее поле в командах, для 3-хадресной ЭВМ имеем следующий текст программы:

11 MUL B, C, T1 / T1← B*C

12 MUL D, E, T2 / T2← D*E

13 ADD T1, T2, Q / Q←T1+ = B*C + D*E

Для двухадресной ЭВМ, которая имеет формат команды, приведенный на рис.1.5, имеем следующее:

MUL B, C / C ← B*C

MUL D, E / E ← D*E

ADD C, E / E←C + E

MOV E,Q / Q←E

К слову сказать, некоторые варианты ВМ размещают результат по адресу не второго, а первого операнда:

| OP | AD1 ADR | AD2 |

Но это различие не принципиально.

Для одноадресной ЭВМ один из операндов перед исполнением команды должен находиться в аккумуляторе. Для этого вводится понятие загрузки аккумулятора. Вводится команда LOAD, LD или специально для загрузки аккумулятора LDA. Также вводится команда выгрузки из аккумулятора «запомнить» - STORE, ST или для аккумулятора STA. Тогда имеем:

LDA B / AC ← B

MUL C / AC← B*C

STA T1 / T1 ← AC

LDA D / AC ← D

MUL E / AC ← AC*D

ADD T1 / AC ← AC + T1 = B*C + D*E

STA Q / Q ← AC = B*C + D*E

Как видим, при уменьшении длины формата команды программа увеличивается в количестве слов, требуемых для выполнения той же функции. Это и понятно, ведь при уменьшении информативности команды (она становится короче) длина программы увеличивается.

Для стековой ЭВМ имеются одноадресные команды загрузки операндов в стек и выгрузки результата, а также безадресные команды выполнения операций.

| E | ||||||||||||||

| C | D | D | D*E | |||||||||||

| B | B | B*C | B*C | B*C | B*C | B*C+ D*E | ||||||||

| PUSH B | PUSH C | MUL | PUSH D | PUSH E | MUL | ADD | POP Q |

Рис.1.8. Пример выполнения вычислений на стековой ВМ

Сравним вычисления на ВМ с различной разрядностью.

Таблица 1.1

| Адресность команды | Длина команды, разрядов | Кол-во строк программы | Длина программы, бит |

| стек |

Анализ таблицы позволяет сказать, что при уменьшении количества полей в команде уменьшается общая длина программы, но увеличивается количество строк программы, поскольку информативность команды падает.

2. Архитектура ВМ

Рассмотрение архитектуры ВМ можно проводить, по крайней мере, двумя путями. Либо рассмотреть конкретную ВМ и строить выводы для других ВМ. Либо рассматривать по порядку, как в учебнике. Будем рассматривать архитектуру ВМ на примере некоторой учебной ВМ, и потом можно будет легче усвоить, как построена любая другая ВМ.

2.1. Логическое проектирование учебной ВМ

Для построения структуры ВМ необходимо выполнить ряд этапов.

1) Выбор системы команд.

Для примера выберем одноадресную ВМ.

2) Разрядность ВМ.

Обычно разрядность выбирают кратной байту – восьми битам. 8 бит для ВМ уже слишком мало. Современные ВМ обычно 32-х или 64-х разрядные. Для упрощения рассмотрения выберем разрядность слова в ВМ 16.

3) Зададим объем памяти ВМ.

Наша ВМ будет универсальная, т.е. предназначенная для широкого круга разнообразных задач. Первые ЭВМ имели память 4К слов. Поэтому для учебной ВМ мы тоже выберем такую память. Естественно, современные ЭВМ имеют память Гигабайт и более.

4) Определимся с разрядностью регистров.

Регистр адреса памяти MAR в соответствии с объемом памяти 4К слов (4К = 212) должен иметь 12 разрядов.

Регистр данных памяти MDR в соответствии с разрядностью слова ВМ должен иметь 16 разрядов.

Формат команды содержит два поля – поле кода операции и поле адреса операнда. Выберем количество команд в нашей учебной ВМ 16. Тогда поле кода операции будет содержать 4 разряда, а поле адреса – 12 разрядов. Всего длина команды соответствует 16 разрядам.

5) Счетчик команд должен иметь возможность адресации во всем объеме памяти ВМ, поэтому содержит 12 разрядов.

6) Регистр команды IR должен содержать саму команду – 16 разрядов.

7) Аккумулятор – соответствует разрядности слова в ВМ – 16 разрядов.

8) Таким образом, в составе ВМ будут иметься регистры: PC, MAR, MDR, IR, AC. Кроме того – регистры ввода и вывода информации InpR и OutR – они обычно длиной 1 байт. Также имеется АЛУ.

С составом ВМ определились. Как соединены составные части ВМ определим позже.

Таблица 2.1. Таблица команд ВМ.

| № и обозначение команды | Команда | Код команды | Адрес | Расшифровка команды | |

| 0 q0 | LDA | AD | AC←M[AD] | ||

| 1 q1 | STA | AD | M[AD] ← AC | ||

| 2 q2 | ADD | AD | AC← AC+ M[AD] | ||

| 3 q3 | SUB | AD | AC← AC- M[AD] | ||

| 4 q4 | AND | AD | AC← AC˄M[AD] | ||

| 5 q5 | OR | AD | AC← AC۷M[AD] | ||

| 6 q6 | XOR | AD | AC← AC  M[AD] M[AD]

| ||

| 7 q7 | COM | AD | AC←  (обратный код) (обратный код)

| ||

| 8 q8 | NEG | AD | AC←

| ||

| 9 q9 | INC | AD | AC←M[AD]+1 | ||

| 10 q10 | DEC | A | AD | AC←M[AD]-1 | |

| 11 q11 | JMP | B | AD | PC←AD (переход) | |

| 12 q12 | CLEA | C | AD=FFF* | AC←0 | |

| 13 q13 | INCA | D | AD=FFF* | AC← AC+1 | |

| 14 q14 | INP | E | AD=FFF* | AC← INPR (ввод) | |

| 15 q15 | OUT | F | AD=FFF* | OUTR ← AC (вывод) | |

Примечание *: AD=FFF означает заполнение единицами адресного поля.

Рассмотрим, как расшифровывается содержимое регистра команд.

Пусть IR = 0011 0001 0010 10002 = 312816

Первое поле длиной 4 разряда – это код команды. В нашем примере команда 3 – это операция вычитания SUB. Остальные 12 разрядов – это адрес ячейки памяти, где находится второй операнд. Первый операнд уже должен находиться в аккумуляторе.

2.2. Центральный процессор

Центральный процессор (ЦП) – главный элемент ВМ, который реализует выполнение команд.

В состав ЦП входят регистры:

PC – счетчик команд;

IR – регистр команды;

AC – аккумулятор;

MAR – регистр адреса памяти;

MDR – регистр данных памяти;

InpR, OutR – регистры ввода и вывода данных;

АЛУ – арифметико-логическое устройство;

M – память.

Все эти устройства входят в состав устройства управления (УУ) и операционного устройства (ОУ) ЦП. Рассмотрим их подробнее.

2.3. ОУ ЦП учебной ВМ

Представим восемь схем полных сумматоров SM с различными входными данными.

| S1 S0 | A | “0” | C0 | A | “0” | C0 | ||

| 0 0 | SM | SM | ||||||

| A | A+1 | |||||||

| A | B | A | B | |||||

| 0 1 | SM | SM | ||||||

| A+B | A+B+1 | |||||||

| A | B | A | B | |||||

| 1 0 | SM | SM | ||||||

| A+ | A+ | |||||||

| A | “1” | A | “1” | |||||

| 1 1 | SM | SM | ||||||

| A-1 | A | |||||||

Здесь “0” и “1” означают развёрнутый ноль и развернутую единицу, то есть ноль или единицу, содержащиеся в каждом разряде слова ВМ. S1 и S0 – это управляющие разряды, характеризующие операцию, которую выполняет сумматор, C0 – перенос в младший разряд сумматора.

На представленных схемах на первый вход сумматоров всегда подается одно и то же число А. На самом деле это не всегда так, что мы покажем впоследствии.

Для усвоения смысла преобразований в АЛУ рассмотрим работу двух небольших цифровых схем.

Цифровой вентиль

Пусть некоторая схема имеет два входа и один выход. Причем если на входе S имеется ноль, то на выходе тоже имеется ноль, если на входе S имеется 1, то выход схемы соответствует входу D.

| S | D | Y |

Фактически эта схема представляет собой известную схему «И». Она представляет собой цифровой вентиль, где один из входов (S) представляет собой разрешающий вход, а другой (D)- информационный.

Рис. 2.1. Схема И.

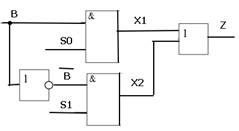

Рис. 2.2. Схема №2.

Таблицу состояний схемы сразу сокращаем, учитывая, что цифровые вентили пропускают на выход либо сигнал B либо его инверсию в зависимости от состояния управляющих входов S0 и S1.

| S1 | S0 | X1 | X2 | Z |

| B | B | |||

|

| |||

| B |

|

При расположении такой схемы в каждом разряде мы имеем выполнение логических функций поразрядно. АЛУ должно обеспечивать выполнение как арифметических, так и логических функций. Условимся, что при значении 1 управляющего сигнала М будут выполняться логические функции, а при значении 0 – арифметические. В качестве логических функций будем рассматривать функции ИЛИ, исключающее ИЛИ, И и инверсию.

Таким образом, АЛУ учебной ВМ выполняет следующие микрооперации в зависимости от значений управляющих входов:

| M | S1 | S0 | C | Микрооперации | Наименование |

| A | Передача А | ||||

| A+1 | Инкремент А | ||||

| A+B | Сумма | ||||

| A+B+1 | Сумма с инкрементом | ||||

| A-B-1 | Разность с декрементом | ||||

| A-B | Разность | ||||

| A-1 | Декремент А | ||||

| A | Передача А | ||||

| Х | A۷B | ИЛИ | |||

| Х | A@B | Исключающее ИЛИ | |||

| Х | A۸B | И | |||

| Х |

| Не А |

С составом ОУ ЦП мы определились ранее. Надо рассмотреть, каким образом все это соединено.

|

|

|

© helpiks.su При использовании или копировании материалов прямая ссылка на сайт обязательна.

|

=A-B-1

=A-B-1 =A-B

=A-B