- Автоматизация

- Антропология

- Археология

- Архитектура

- Биология

- Ботаника

- Бухгалтерия

- Военная наука

- Генетика

- География

- Геология

- Демография

- Деревообработка

- Журналистика

- Зоология

- Изобретательство

- Информатика

- Искусство

- История

- Кинематография

- Компьютеризация

- Косметика

- Кулинария

- Культура

- Лексикология

- Лингвистика

- Литература

- Логика

- Маркетинг

- Математика

- Материаловедение

- Медицина

- Менеджмент

- Металлургия

- Метрология

- Механика

- Музыка

- Науковедение

- Образование

- Охрана Труда

- Педагогика

- Полиграфия

- Политология

- Право

- Предпринимательство

- Приборостроение

- Программирование

- Производство

- Промышленность

- Психология

- Радиосвязь

- Религия

- Риторика

- Социология

- Спорт

- Стандартизация

- Статистика

- Строительство

- Технологии

- Торговля

- Транспорт

- Фармакология

- Физика

- Физиология

- Философия

- Финансы

- Химия

- Хозяйство

- Черчение

- Экология

- Экономика

- Электроника

- Электротехника

- Энергетика

Лабораторная работа №2.

Задание: спроектировать и реализовать дешифратор / мультиплексор / счетчик.

Цель: закрепление навыков работы с САПР Xilinx ISE Design Suite Webpack 10. 1, modelsim 6. 4. b XE; реализация дешифраторов / мультиплексоров / счетчиков на языке VHDL.

Дешифратор:

Таблица 2 – Задание на лабораторную работу

| Вариант | Дешифратор | |

| 3 в 5 | синхронный |

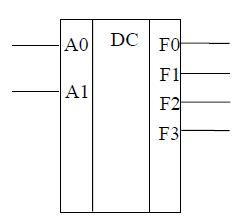

Рисунок 3 – УГО дешифратора.

Листинг программы:

-- Create Date: 14: 06: 39 05/07/2012

-- Design Name:

-- Module Name: desh-Dehavioral

-- Project Name: laba2_1

desh. ucf:

#inputs

NET " A[3]" LOC = J13;

NET " A[2]" LOC = K14;

NET " A[1]" LOC = K13;

#outputs

NET " F[5]" LOC = N14;

NET " F[4]" LOC = P13;

NET " F[3]" LOC = N12;

NET " F[2]" LOC = P12;

NET " F[1]" LOC = P11;

desh. vhd:

LIBRARY ieee;

USE ieee. std_logic_1164. ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--USE ieee. numeric_std. ALL;

ENTITY test IS

END test;

ARCHITECTURE behavior OF test IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT decode

PORT(

A: IN std_logic_vector(2 downto 0);

F: OUT std_logic_vector(4 downto 0);

clock: IN std_logic

);

END COMPONENT;

--Inputs

signal A: std_logic_vector(2 downto 0): = (others => '0');

signal clock: std_logic: = '0';

--Outputs

signal F: std_logic_vector(4 downto 0);

-- Clock period definitions

constant clock_period: time: = 10 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: decode PORT MAP (

A => A,

F => F,

clock => clock

);

-- Clock process definitions

clock_process: process

begin

clock < = '0';

wait for clock_period/2;

clock < = '1';

wait for clock_period/2;

end process;

-- Stimulus process

stim_proc: process

begin

-- hold reset state for 100 ns.

wait for 100 ns;

A< =" 000";

wait for clock_period*10;

A< =" 001";

wait for clock_period*10;

A< =" 100";

wait for clock_period*10;

A< =" 010";

wait for clock_period*10;

A< =" 011";

-- insert stimulus here

wait;

end process;

END;

library IEEE;

use IEEE. std_logic_1164. all;

entity decode is

port ( A: in std_logic_vector (2 downto 0 );

F: out std_logic_vector (4 downto 0);

clock: in std_logic);

end decode;

architecture decode_arch of decode is

begin

process (clock)

begin

if clock'event and clock='0' then

case A is

when " 000" => F < =" 00001";

when " 001" => F < =" 00010";

when " 100" => F < =" 00100";

when " 010" => F < =" 01000";

when " 011" => F < =" 10000";

when others => F < = " 11000";

end case;

end if;

end process;

end decode_arch;

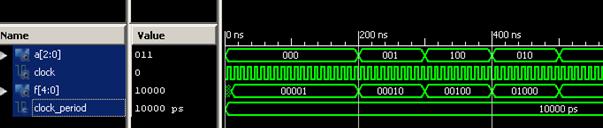

Рисунок 4 – Временная диаграмма работы дешифратора.

Смотря какие двоичные коды подаются на входы А, получаются одноединичный код на выходе. В зависимости от того какие переключатели будут включены (коды от 000 до 111), так и будут загораться светодиоды

Мультиплексор:

Таблица 3 – Задание на лабораторную работу

| Вариант | Количество информационных входов | Комбинации на информационных входах |

| “10101”; “10001”; “10010”; “11011”; “10111”; “01001”; |

Рисунок 5 – УГО мультиплексора.

- Create Date: 14: 34: 20 05/18/2012

-- Design Name:

-- Module Name: Multy - Behavioral

-- Project Name:

mult. vhd:

library IEEE;

use IEEE. STD_LOGIC_1164. ALL;

entity Multy is

Port ( pinin: in std_logic_vector (2 downto 0);

pinout: out std_logic_vector (4 downto 0)

);

end Multy;

architecture Behavioral of Multy is

begin

process (pinin)

begin

case pinin is

when " 000" => pinout < =" 10101";

when " 001" => pinout < =" 10001";

when " 010" => pinout < =" 10010";

when " 011" => pinout < =" 11011";

when " 100" => pinout < =" 10111";

when others => pinout < =" 01001";

end case;

end process;

end Behavioral;

qq. ucf:

#inputs

NET pinin(0) LOC = F12;

NET pinin(1) LOC = G12;

NET pinin(2) LOC = H14;

#outputs

NET pinout(0) LOC = K12;

NET pinout(1) LOC = P14;

NET pinout(2) LOC = L12;

NET pinout(3) LOC = N14;

NET pinout(4) LOC = P13;

Test. vhd

LIBRARY ieee;

use IEEE. numeric_std. all;

use IEEE. std_logic_unsigned. all;

USE ieee. std_logic_1164. ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--USE ieee. numeric_std. ALL;

ENTITY Test IS

END Test;

ARCHITECTURE behavior OF Test IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT Multy

PORT(

pinin: IN std_logic_vector (2 downto 0);

pinout: OUT std_logic_vector (4 downto 0)

);

END COMPONENT;

signal pinin: std_logic_vector(2 downto 0): = (others => '0');

--Outputs

signal pinout: std_logic_vector(4 downto 0);

-- No clocks detected in port list. Replace < clock> below with

-- appropriate port name

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: Multy PORT MAP (

pinin => pinin,

pinout=> pinout

);

-- Stimulus process

stim_proc: process

begin

-- hold reset state for 100 ns.

wait for 100 ns;

pinin < = " 000";

for i in 0 to 4 loop

pinin < = pinin + '1';

wait for 50 ns;

end loop;

wait;

end process;

END;

Рисунок 6 – Временная диаграмма работы мультиплексора.

Смотря какие сигналы поданы на входы I, на выходе получаются сигналы в соответствии с вариантом. На вход мультиплексора с поступают двоичные числа. Состояние светодиодов зависит от положения переключателей.

Счетчик:

Таблица 4 – Соответствие выводов микросхемы и их соответствие FPGA pin

| Выходы счетчика | ||||||||

| clk | out0 | out1 | out2 | out3 | out4 | out5 | out6 | out 7 |

| LD7 | LD6 | LD5 | LD4 | LD3 | LD2 | LD1 | LD0 | |

| Т9 | P11 | P12 | N12 | P13 | N14 | L12 | P14 | K12 |

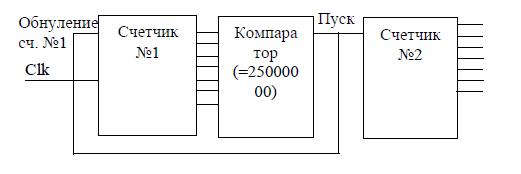

Рисунок 7 – Схема заданного счетчика.

-- Create Date: 12: 34: 29 05/22/2012

-- Design Name:

-- Module Name: CounterM - Behavioral

CounterM. vhd:

library IEEE;

use IEEE. STD_LOGIC_1164. ALL;

use IEEE. STD_LOGIC_ARITH. ALL;

use IEEE. STD_LOGIC_UNSIGNED. ALL;

entity CounterM is

Port ( CLK: in STD_LOGIC;

F: out STD_LOGIC_Vector(0 to 7));

end CounterM;

architecture Behavioral of CounterM is

begin

Process (CLK)

variable St1: integer: =0;

variable St2: STD_LOGIC_Vector(0 to 7): =" 00000000";

begin

if (CLK' event and CLK='1') then

St1: = St1 + 1;

if (St1 = 25000000) then St1: =0;

St2: =St2+" 00000001";

F< =St2;

end if;

end if;

End process;

end Behavioral;

CounterU. ucf:

#inputs --перечисление входов

NET " CLK" LOC = T9;

#outputs --перечисление выходов

NET " F[0]" LOC = P11;

NET " F[1]" LOC = P12;

NET " F[2]" LOC = N12;

NET " F[3]" LOC = P13;

NET " F[4]" LOC = N14;

NET " F[5]" LOC = L12;

NET " F[6]" LOC = P14;

NET " F[7]" LOC = K12;

Рисунок 8 - Временная диаграмма работы счетчика.

Счетчик реализует инкремент по тактовому сигналу CLK = 50 МГц. При достижении двоичной комбинации эквивалентной десятичному числу 25 000 000 счетчик обнуляется и подается тактовый сигнал, по которому происходит инкремент второго восьмиразрядного счетчика. Т. к. выходы второго счетчика подключены к светодиодам, то каждые полсекунды на светодиодах будет отображаться текущее двоичное число, отсчитанное вторым счетчиком.

Вывод: были закреплены навыки работы с САПР Xilinx ISE Design Suite Webpack 10. 1, modelsim 6. 4. b XE; реализованы дешифратор, мультиплексор и счетчик на языке VHDL.

|

|

|

© helpiks.su При использовании или копировании материалов прямая ссылка на сайт обязательна.

|