- Автоматизация

- Антропология

- Археология

- Архитектура

- Биология

- Ботаника

- Бухгалтерия

- Военная наука

- Генетика

- География

- Геология

- Демография

- Деревообработка

- Журналистика

- Зоология

- Изобретательство

- Информатика

- Искусство

- История

- Кинематография

- Компьютеризация

- Косметика

- Кулинария

- Культура

- Лексикология

- Лингвистика

- Литература

- Логика

- Маркетинг

- Математика

- Материаловедение

- Медицина

- Менеджмент

- Металлургия

- Метрология

- Механика

- Музыка

- Науковедение

- Образование

- Охрана Труда

- Педагогика

- Полиграфия

- Политология

- Право

- Предпринимательство

- Приборостроение

- Программирование

- Производство

- Промышленность

- Психология

- Радиосвязь

- Религия

- Риторика

- Социология

- Спорт

- Стандартизация

- Статистика

- Строительство

- Технологии

- Торговля

- Транспорт

- Фармакология

- Физика

- Физиология

- Философия

- Финансы

- Химия

- Хозяйство

- Черчение

- Экология

- Экономика

- Электроника

- Электротехника

- Энергетика

c: out bit);

Міністерство освіти та науки

Національний авіаційний університет

Кафедра електроніки

Лабораторна робота №1

З предмету: «Мови опису мікро- та наноелектросхем»

Тема: «Опис логічних операцій на VHDL»

Виконав:

студент групи МН-414

Кашуба Віталій

Перевірив:

Миколушко А. М.

Київ-2015

Мета: за допомогою мови опису VHDL виконати елементарні логічні операції.

Для виконання даної лабораторної роботи я використав середовище

Quartus II 9. 1.

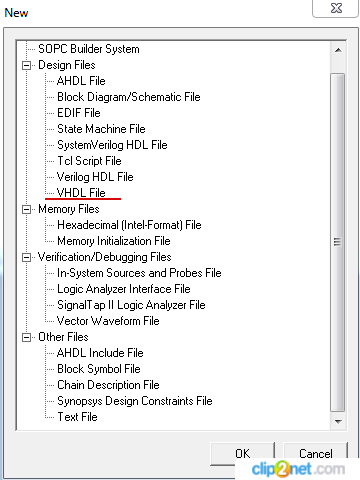

Для створення проекту вибираємо New/VHDL File.

Після чого називаємо наш проект та вибираємо папку для збереження.

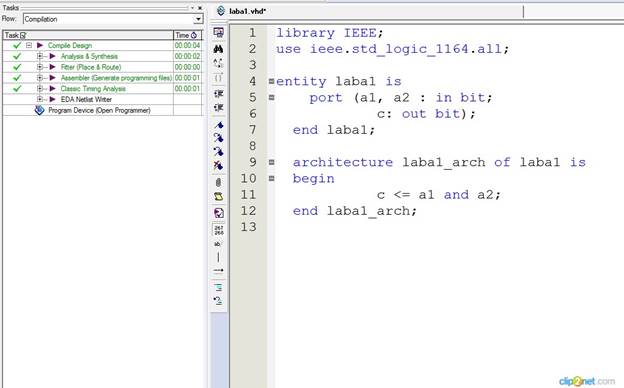

Далі у нас появиться вікно редактора в якому ми опишемо логічні операції.

library IEEE; /підключимо основну стандартизовану

бібліотеку для опису апаратних приладів;

use ieee. std_logic_1164. all; /використаємо дану бібліотеку для нашого

коду;

Дальше необхідно зробити опис об’єкта «в цілому» відомий як опис інтерфейсу(entity).

entity laba1 is / створюємо назву об’єкту;

port (a1, a2: in bit; / декларація вхідного порту in та вихідного

порту out (бітовий тип даних);

c: out bit);

end laba1; / закінчення опису інтерфейсу;

Наступним кроком буде опис архітектури об’єкта.

architecture laba1_arch of laba1 is /створюємо назву архітектури в

об’єкті laba1 раніше названій;

begin / починаємо опис архітектури;

c < = a1 and a2; / описуємо логічну операцію І;

end laba1_arch; / закінчуємо опис;

В результаті отримуємо:

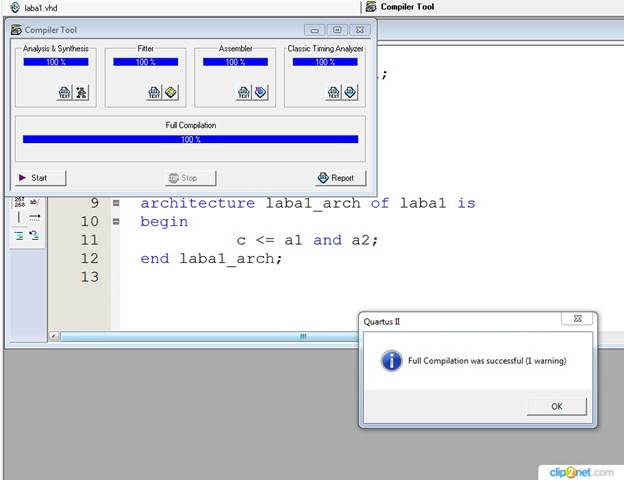

Відкомпілюємо дану логічну операцію. Для цього в меню Processing знаходимо Start Compilation і проводимо компіляцію. (Для швидкого компілювання Ctrl+L).

Після компіляції отримуємо:

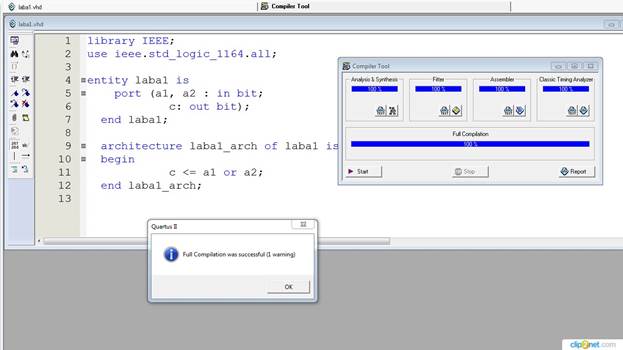

Для того щоб виконати інші логічні операції, замінюємо назву логічної функції в архітектурі об’єкту.

Операція or.

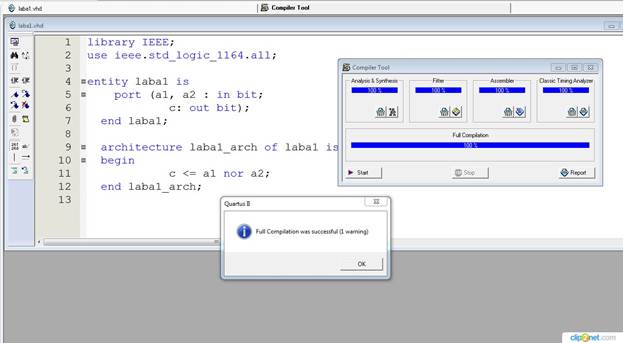

Операція nor.

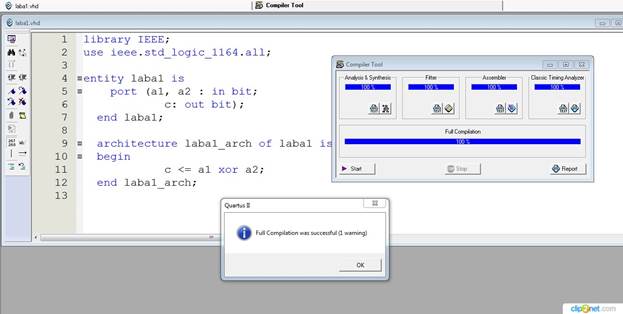

Операція xor.

1 warning – просте попередження про використання засувок (latches), які не впливають на дизайн опису. В даній лабораторній роботі я використав засувку MX7000B.

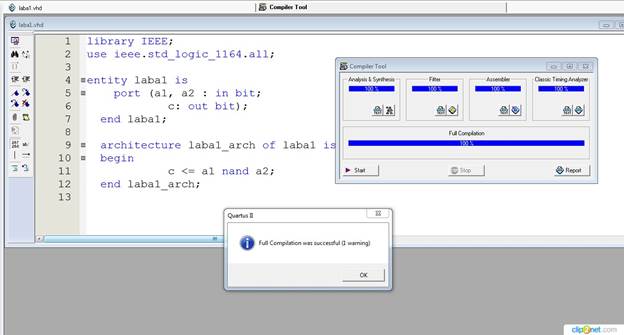

Операція nand.

Для повної перевірки можна використати Model Sim Altera.

Висновок. Виконавши дану лабораторну роботу, я ознайомився із мовою опису для схемотехніки, освоїв базовий синтаксис та пунктуацію даної мови, розробив та прокомпілював прості логічні оператори and, or, xor, nor, nand.

|

|

|

© helpiks.su При использовании или копировании материалов прямая ссылка на сайт обязательна.

|