- Автоматизация

- Антропология

- Археология

- Архитектура

- Биология

- Ботаника

- Бухгалтерия

- Военная наука

- Генетика

- География

- Геология

- Демография

- Деревообработка

- Журналистика

- Зоология

- Изобретательство

- Информатика

- Искусство

- История

- Кинематография

- Компьютеризация

- Косметика

- Кулинария

- Культура

- Лексикология

- Лингвистика

- Литература

- Логика

- Маркетинг

- Математика

- Материаловедение

- Медицина

- Менеджмент

- Металлургия

- Метрология

- Механика

- Музыка

- Науковедение

- Образование

- Охрана Труда

- Педагогика

- Полиграфия

- Политология

- Право

- Предпринимательство

- Приборостроение

- Программирование

- Производство

- Промышленность

- Психология

- Радиосвязь

- Религия

- Риторика

- Социология

- Спорт

- Стандартизация

- Статистика

- Строительство

- Технологии

- Торговля

- Транспорт

- Фармакология

- Физика

- Физиология

- Философия

- Финансы

- Химия

- Хозяйство

- Черчение

- Экология

- Экономика

- Электроника

- Электротехника

- Энергетика

Синхронный RSС. По способу приема информации триггеры делятся на синхронные и асинхронные.. Асинхронные триггеры реагируют на информационные сигналы в момент их появления на входах, а синхронные реагируют на информационные сигналы только при наличии разре

Синхронный RSС

По способу приема информации триггеры делятся на синхронные и асинхронные.

Асинхронные триггеры реагируют на информационные сигналы в момент их появления на входах, а синхронные реагируют на информационные сигналы только при наличии разрешающего сигнала на специальном синхровходе.

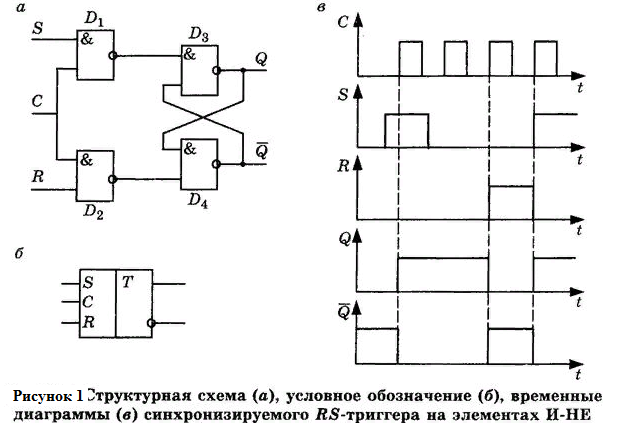

Синхронный RSС -триггер отличается от асинхронного наличием С-входа для синхронизирующих (тактовых) импульсов. Он состоит из асинхронного (рисунок1) и двух логических элементов на входе.

При С=0 входные логические элементы блокированы, их состояния не зависят от сигналов на S и R - входах и соответствуют 0. RS-триггер будет в режиме хранения записанной информации. При С=1 входные логические элементы открыты для восприятия информационных сигналов и передачи их на входы синхронного триггера.

Синхронные триггеры в свою очередь делятся на триггеры со статическим и динамическим управлением. Триггеры со статическим управлением реагируют при подаче на синхровход сигнала 1 (прямой статический) или 0 (инверсный) входы. Триггеры с динамическим управлением реагируют на изменения сигнала на синхровходе от 0 к 1 (прямой динамический) или от 1 к 0 (инверсный динамический).

D-триггер. D-триггер имеет один информационный вход; сигнал на выходе D-триггера повторяет сигнал на входе D, существовавший в предыдущем такте, т. е. D-триггер «запоминает» этот сигнал до следующего такта.

D-триггер задерживает на один такт информацию, существовавшую на входе D.

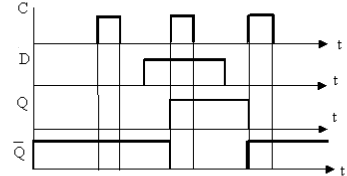

D-триггеры выполняются тактируемыми. Логическая структура D-триггера с тактированием потенциалом (уровнем) синхронизирующего сигнала, представлена на рисунке 2

Рисунок 2. Структурная схема и таблица функционирования D-триггера

Принцип действия рассматриваемого D-триггера поясняется диаграммами сигналов, приведенными на рисунке 2

Рисунок 3. Диаграммы сигналов D-триггера

Из диаграмм видно, что D-триггер осуществляет «задержку» появления, (исчезновения) импульса на выходе на промежутки времени между фронтом импульса и фронтом (спадом) сигнала на D-входе.

D-триггеры очень часто используются в различных схемах: регистрах, счетчиках.

Т-триггер. Т-триггер − это логическая схема с двумя устойчивыми состояниями и одним информационным входом, изменяющая свое состояние на противоположное всякий раз, когда на вход Т поступает управляющий сигнал.

Т-триггер называют также счетным триггером (триггером со счетным входом). Его применяют в основном для счета входных импульсов и деления частоты этих импульсов. Применение Т-триггеров в счетчиках обусловлено тем, что каждому входному импульсу соответствует одно срабатывание, т. е. число срабатываний триггера соот-

ветствует числу импульсов.

Деление частоты Т-триггером следует из принципа его действия.

Импульсы на выходе Т-триггера имеют равные длительность паузы и ширину импульса независимо от скважности входного периодического сигнала. Последовательность таких импульсов называют меандром. Диаграммы сигналов и таблица состояний Т-триггера

показаны на рисунке 4.

Рисунок 4. Диаграммы сигналов и таблица состояний Т-триггера

Самостоятельных Т-триггеров не выпускают.

Под делителем частоты понимается устройство, осуществляющее изменение частоты сигнала на выходе по отношению к входному сигналу в n раз. Параметр n, определяемый отношение частоты сигнала на входе и выходе устройства, называется коэффициентом деления. На каждые n-импульсов на входе схемы формируется один импульс на выходе.

Он построен на D-триггере. Для того, чтобы перевести D-триггер в счетный режим, нужно соединить инверсный выход триггера Q с его D-входом, так как это показано на рисунке 5.

Рисунок 5. Простейший делитель частоты.

Рассмотрим подробнее работу этой схемы. Предположим, что после включения триггер установился в единичное состояние. Это означает, что на инверсном выходе триггера (Q) присутствует логический ноль. Этот ноль поступает на D-вход. Подадим на вход делителя некоторый цифровой сигнал. По фронту первого входного импульса D-триггер перейдет в нулевое состояние, так как на его D-входе сигнал логического нуля. После этого на инверсном выходе триггера устанавливается логическая единица. Поэтому по фронту следующего входного импульса триггер переключится в единичное состояние.

И так далее.

Контрольные вопросы:

1. На каких элементах можно построить RSС-триггер

2. При каких состояниях входов триггера на его выходе установится логическая единица

3. При каких состояниях входов триггера на его выходе установится логический ноль

4. Основное назначение D-триггера.

5. Когда происходит переключение динамического D-триггера.

6. На каких элементах строится D-триггер

7. Перечислите все режимы работы D-триггера.

|

|

|

© helpiks.su При использовании или копировании материалов прямая ссылка на сайт обязательна.

|