- Автоматизация

- Антропология

- Археология

- Архитектура

- Биология

- Ботаника

- Бухгалтерия

- Военная наука

- Генетика

- География

- Геология

- Демография

- Деревообработка

- Журналистика

- Зоология

- Изобретательство

- Информатика

- Искусство

- История

- Кинематография

- Компьютеризация

- Косметика

- Кулинария

- Культура

- Лексикология

- Лингвистика

- Литература

- Логика

- Маркетинг

- Математика

- Материаловедение

- Медицина

- Менеджмент

- Металлургия

- Метрология

- Механика

- Музыка

- Науковедение

- Образование

- Охрана Труда

- Педагогика

- Полиграфия

- Политология

- Право

- Предпринимательство

- Приборостроение

- Программирование

- Производство

- Промышленность

- Психология

- Радиосвязь

- Религия

- Риторика

- Социология

- Спорт

- Стандартизация

- Статистика

- Строительство

- Технологии

- Торговля

- Транспорт

- Фармакология

- Физика

- Физиология

- Философия

- Финансы

- Химия

- Хозяйство

- Черчение

- Экология

- Экономика

- Электроника

- Электротехника

- Энергетика

Лабораторная работа 22

|

Федеральное государственное бюджетное образовательное учреждение высшего образования | |||||||

Институт кибернетики

Кафедра программного обеспечения систем радиоэлектронной аппаратуры

Лабораторная работа 22

по курсу «Системы автоматизированного проектирования»

Студент группы КМБО-02-16 Гибшман П.Е.

Преподаватель Коновалова И.В.

МОСКВА 2020

1) Постановка задачи:

Разработать сдвиговый регистр с параллельной загрузкой и схему вычисления n-ого импульса при помощи счётчика.

2) Реализация сдвигового регистра с параллельной загрузкой:

| 1 2 3 4 5 6 7 8 9101112131415161718192021222324 | module verilog_3_1(input LOAD,input [3:0]data,input D_in,input clk,output reg [3:0] Q); always@ (posedge clk)if (LOAD)begin Q[3] <= data[3]; Q[2] <= data[2]; Q[1] <= data[1]; Q[0] <= data[0];endelsebegin Q[3] <= Q[2]; Q[2] <= Q[1]; Q[1] <= Q[0]; Q[0] <= D_in;end endmodule |

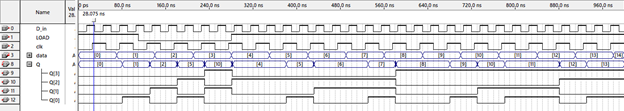

Результат моделирования:

3) Реализация схемы вычисления n-ого импульса при помощи счётчика:

| 1 2 3 4 5 6 7 8 910111213141516171819202122232425 | module verilog_3_2(input [7:0]n,input clk,output reg [7:0] Q,output out_wire,output reg out_reg); initial Q = 0;assign out_wire = out_reg; always@ (posedge clk)begin if (Q==n) begin Q = 0; out_reg = 1; end else begin out_reg = 0; Q <= Q + 1; endend endmodule |

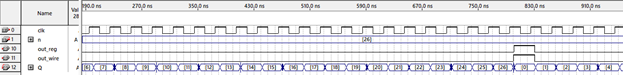

Результат моделирования:

4) Вывод

Результат моделирования соответствует ожиданиям.

|

|

|

© helpiks.su При использовании или копировании материалов прямая ссылка на сайт обязательна.

|