- Автоматизация

- Антропология

- Археология

- Архитектура

- Биология

- Ботаника

- Бухгалтерия

- Военная наука

- Генетика

- География

- Геология

- Демография

- Деревообработка

- Журналистика

- Зоология

- Изобретательство

- Информатика

- Искусство

- История

- Кинематография

- Компьютеризация

- Косметика

- Кулинария

- Культура

- Лексикология

- Лингвистика

- Литература

- Логика

- Маркетинг

- Математика

- Материаловедение

- Медицина

- Менеджмент

- Металлургия

- Метрология

- Механика

- Музыка

- Науковедение

- Образование

- Охрана Труда

- Педагогика

- Полиграфия

- Политология

- Право

- Предпринимательство

- Приборостроение

- Программирование

- Производство

- Промышленность

- Психология

- Радиосвязь

- Религия

- Риторика

- Социология

- Спорт

- Стандартизация

- Статистика

- Строительство

- Технологии

- Торговля

- Транспорт

- Фармакология

- Физика

- Физиология

- Философия

- Финансы

- Химия

- Хозяйство

- Черчение

- Экология

- Экономика

- Электроника

- Электротехника

- Энергетика

ИССЛЕДОВАНИЕ ФУНКЦИОНИРОВАНИЯ ТРИГГЕРОВ РАЗЛИЧНЫХ ТИПОВ»

МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ УКРАИНЫ

ХАРЬКОВСКИЙ НАЦИОНАЛЬНЫЙ УНИВЕРСИТЕТ РАДИОЭЛЕКТРОНИКИ

Кафедра АПВТ

ОТЧЕТ

по лабораторной работе №4 на тему:

«ИССЛЕДОВАНИЕ ФУНКЦИОНИРОВАНИЯ ТРИГГЕРОВ РАЗЛИЧНЫХ ТИПОВ»

по курсу «Прикладная теория цифровых автоматов»

Вариант №14

Выполнил:

ст. гр. КИ-10-2

Коденко А.В.

Харьков 2011

4.1 Цель работы

Изучить законы функционирования элементарных автоматов, способы их задания; получить навыки составления таблиц переходов и матриц переходов триггерных схем.

4.2 Порядок выполнения работы (Часть 1)

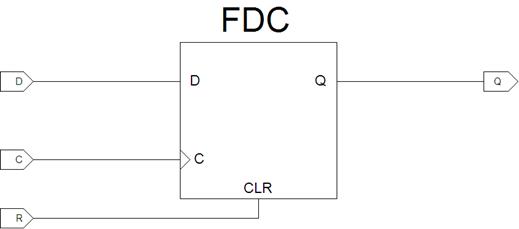

4.2.1 Условное графическое изображение проектируемой комбинационной схемы

4.2.2 Таблица истинности проектируемого устройства

| С | R | D | Q(t+1) |

| E | |||

| E | |||

| X | |||

| X | 0 | ||

| На ост. | Q(t) | ||

4.2.3 VHDL-описание комбинационной схемы устройства

library IEEE;

use IEEE.std_logic_1164.all;

entity D_ff_aR is

port (D: in STD_LOGIC;

C:in STD_LOGIC;

R: in STD_LOGIC;

Q: out STD_LOGIC);

end D_ff_aR;

architecture D_ff_aR of D_ff_aR is

begin

process(C, R) is

begin

if (R ='1') then Q<='0'; --асинхронный сброс в 0 (R - инверсный)

elsif (C'event and C='1') then Q<=D;

end if;

end process;

end D_ff_aR;

4.2.4 Листинг UCF файла

NET "R" LOC = "H18";

NET "D" LOC = "L14";

NET "Q" LOC = "F12";

NET "C" LOC = "N17";

NET "R" CLOCK_DEDICATED_ROUTE = FALSE;

NET "C" CLOCK_DEDICATED_ROUTE = FALSE;

NET "D" CLOCK_DEDICATED_ROUTE = FALSE;

NET "Q" CLOCK_DEDICATED_ROUTE = FALSE;

4.2.5 Результаты автоматизированного синтеза проекта в виде графического отображения схемы преобразователя:

|

|

|

© helpiks.su При использовании или копировании материалов прямая ссылка на сайт обязательна.

|