- Автоматизация

- Антропология

- Археология

- Архитектура

- Биология

- Ботаника

- Бухгалтерия

- Военная наука

- Генетика

- География

- Геология

- Демография

- Деревообработка

- Журналистика

- Зоология

- Изобретательство

- Информатика

- Искусство

- История

- Кинематография

- Компьютеризация

- Косметика

- Кулинария

- Культура

- Лексикология

- Лингвистика

- Литература

- Логика

- Маркетинг

- Математика

- Материаловедение

- Медицина

- Менеджмент

- Металлургия

- Метрология

- Механика

- Музыка

- Науковедение

- Образование

- Охрана Труда

- Педагогика

- Полиграфия

- Политология

- Право

- Предпринимательство

- Приборостроение

- Программирование

- Производство

- Промышленность

- Психология

- Радиосвязь

- Религия

- Риторика

- Социология

- Спорт

- Стандартизация

- Статистика

- Строительство

- Технологии

- Торговля

- Транспорт

- Фармакология

- Физика

- Физиология

- Философия

- Финансы

- Химия

- Хозяйство

- Черчение

- Экология

- Экономика

- Электроника

- Электротехника

- Энергетика

ОГЛАВЛЕНИЕ

ОГЛАВЛЕНИЕ

Структура ПЭВМ типа IBM РС/АТ-286........................................................... Лист 0.

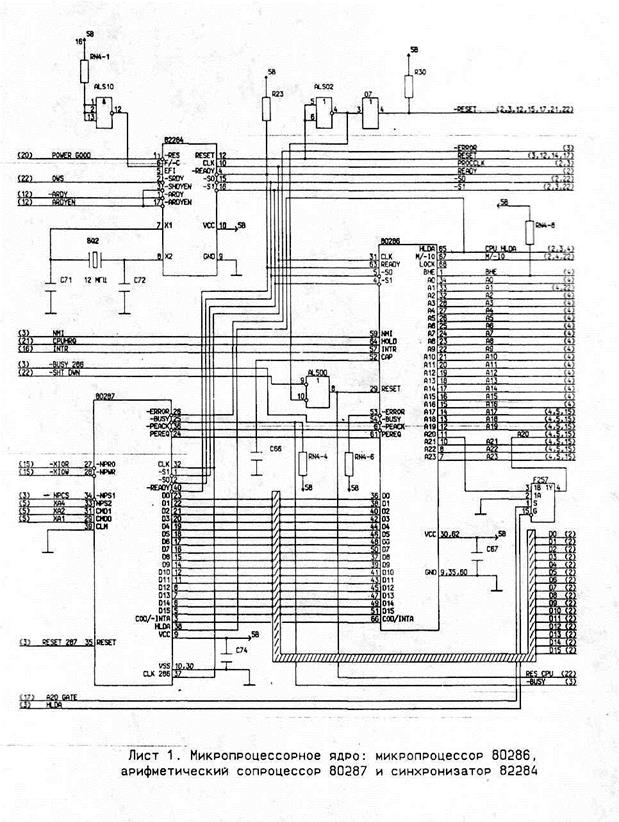

Микропроцессорное ядро: микропроцессор i80286, арифмети-

ческий сопроцессор 80287 и синхронизатор 82284........................................... Лист 1.

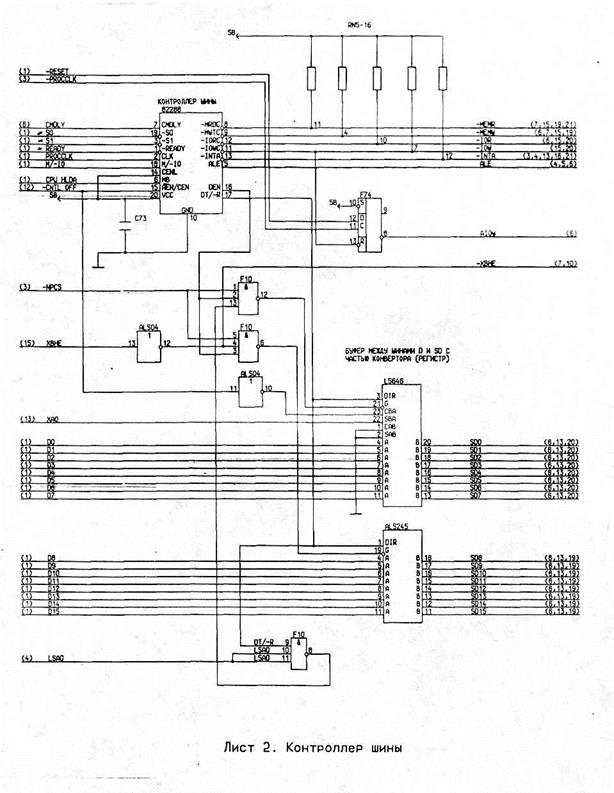

Контроллер шины................................................................................................ Лист 2.

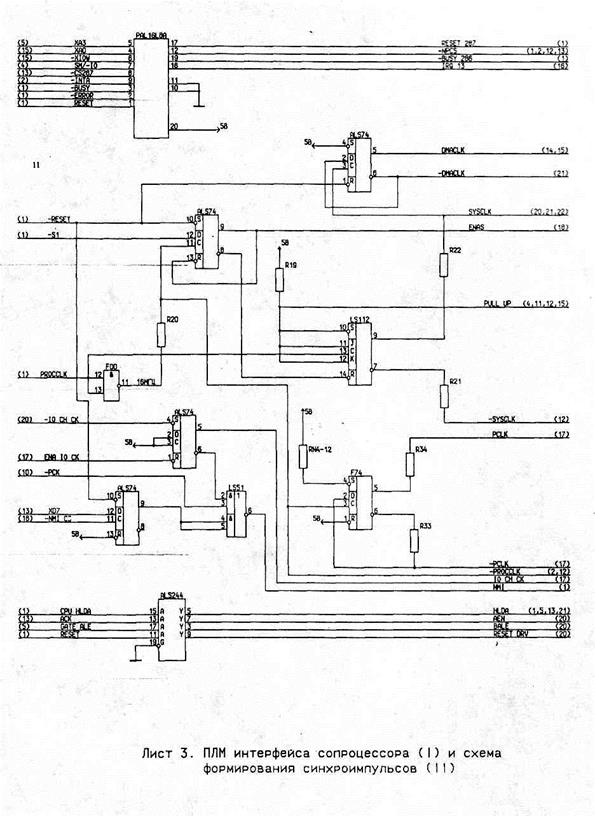

IIЛM интерфейса сопроцессора и схема формирования син-

хроимпульсов........................................................................................................... Лист 3.

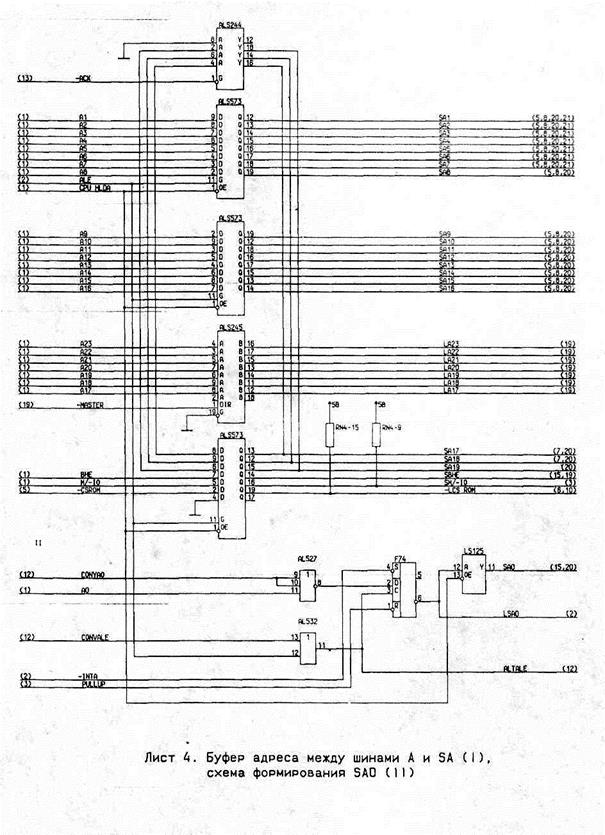

Буфер адреса между шинами А и SA, схема формирования

сигнала SA0.......................................................................................................... Лист 4.

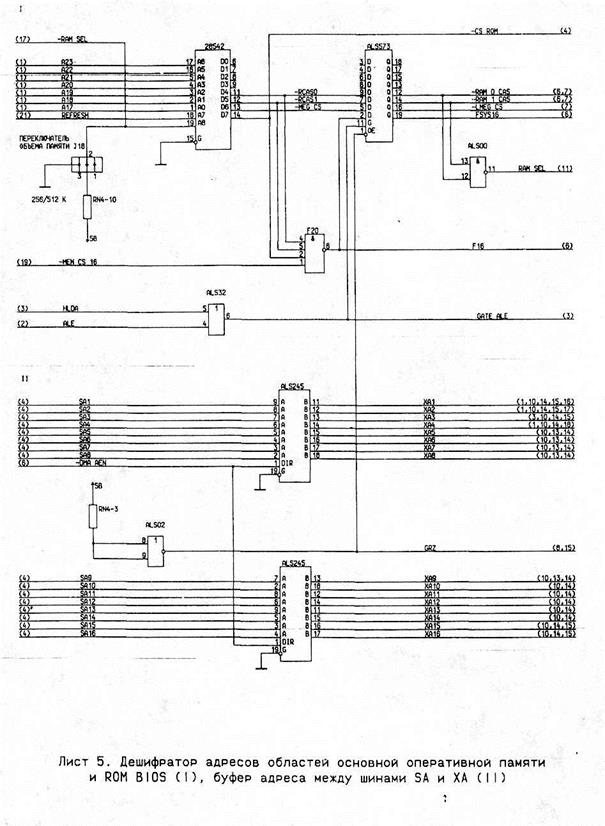

Дешифратор адреса областей основной оперативной памяти

и ROM BIOS, буфер адреса между шинами SA и ХА...................................... Лист 5.

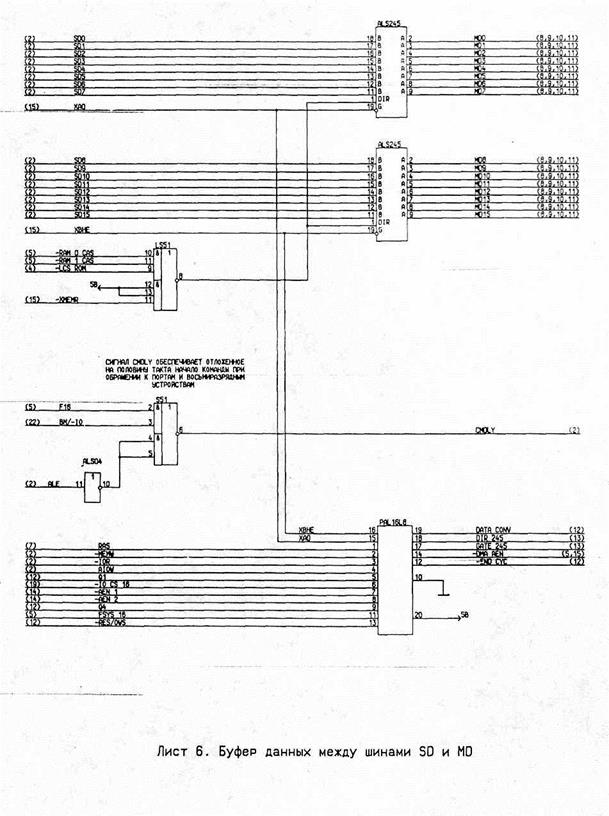

Буфер данных между шинами SD и MD, ПЛМ конвертора.... Лист 6.

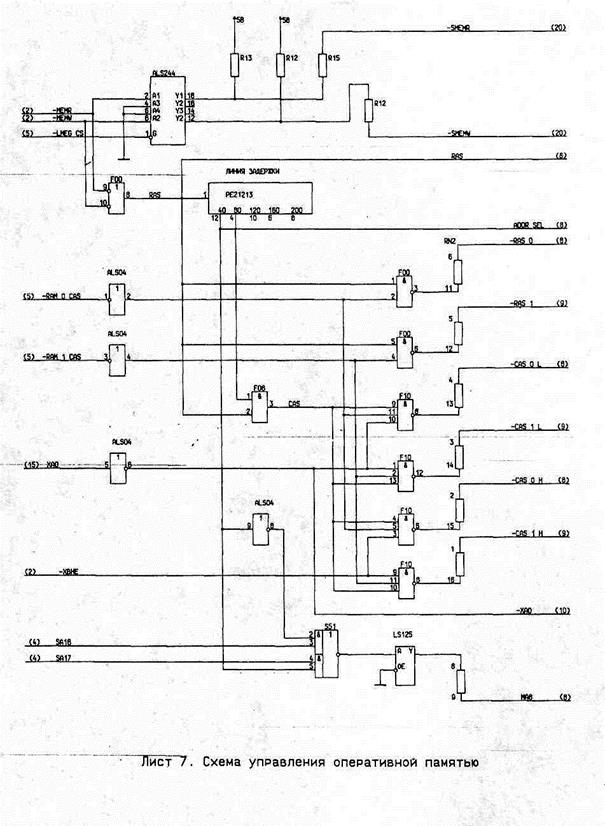

Схема управления оперативной памятью.......................................................... Лист 7.

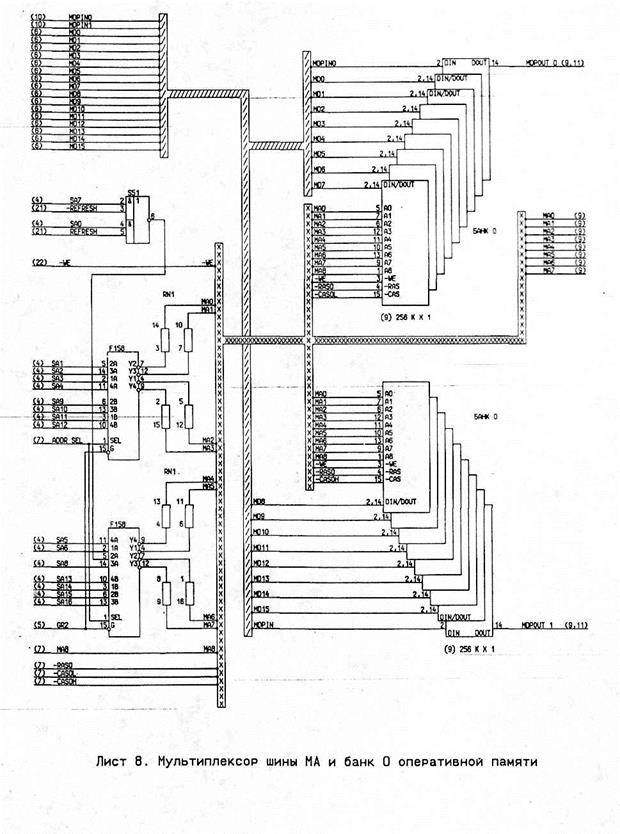

Мультиплексор адресной шины МА оперативной памяти и

Банк 0 оперативной памяти (банк с организацией 256Кх16

с возможностью побайтного обращения к 16-разр-ой строке). Лист 8.

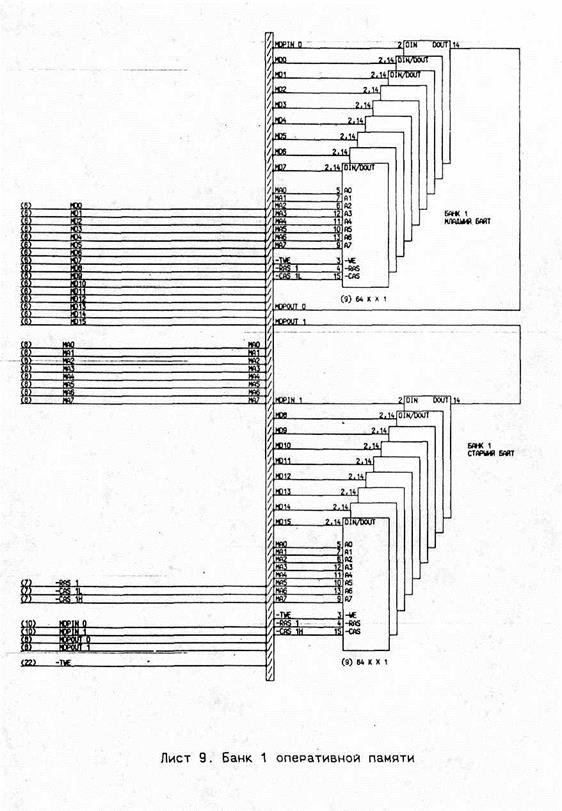

Банк 1 оперативной памяти (банк с организацией 64Кх16

с возможностью побайтного обращения к 16-разр-ой строке). Лист 9.

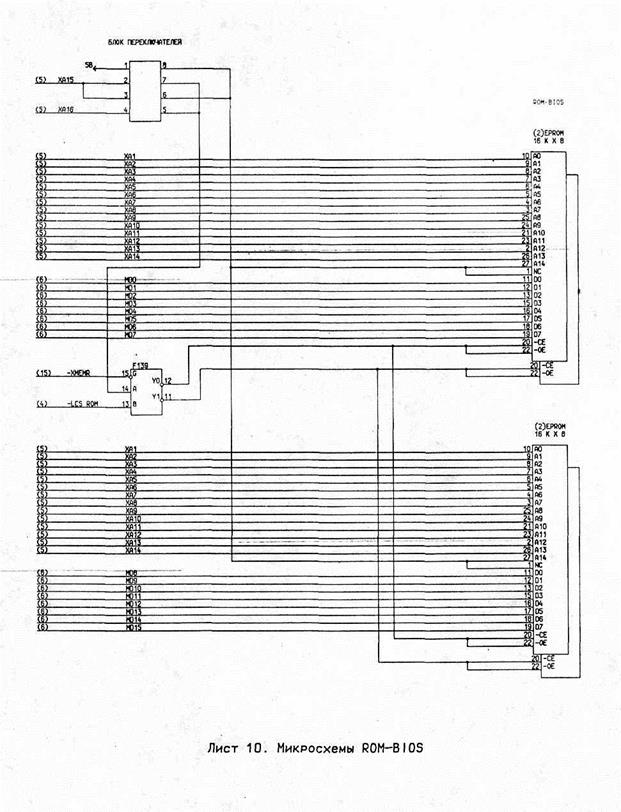

Микросхемы ROM-BIOS (модуль системного ПЗУ)...................................... Лист 10.

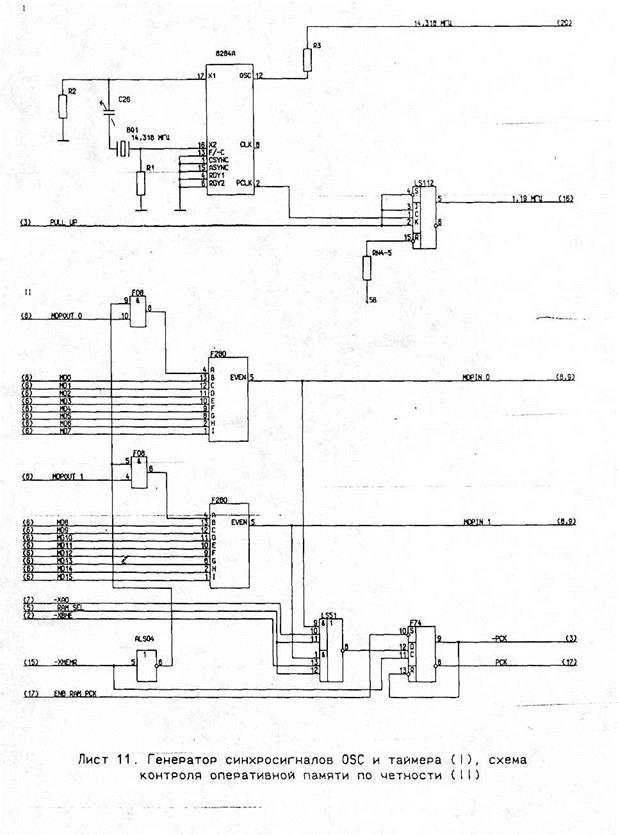

Генератор, синхросигналов ОSC и таймера, схема контро-

ля оперативной памяти по четности................................................................. Лист 11.

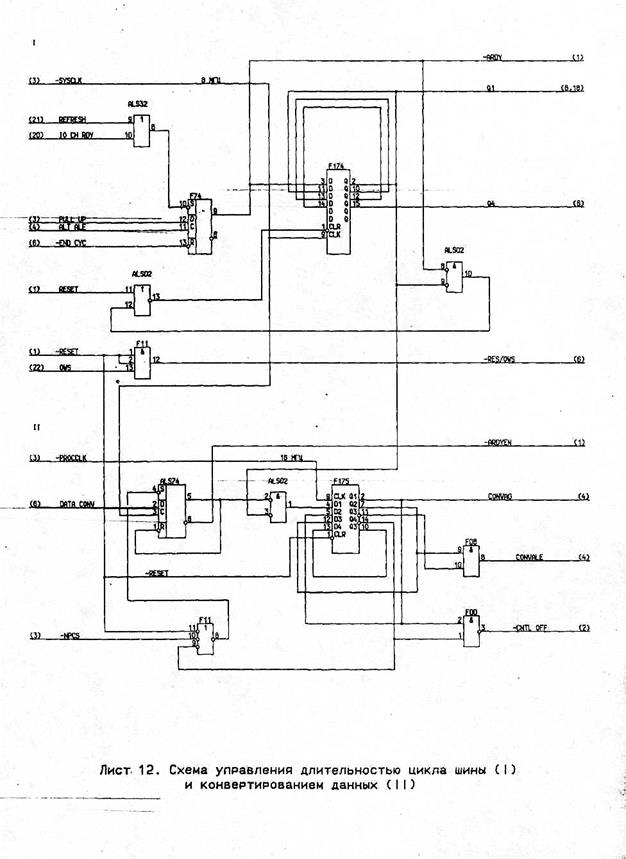

Схема управления длительностью цикла шины и конверти-

рованием данных.................................................................................................... Лист 12.

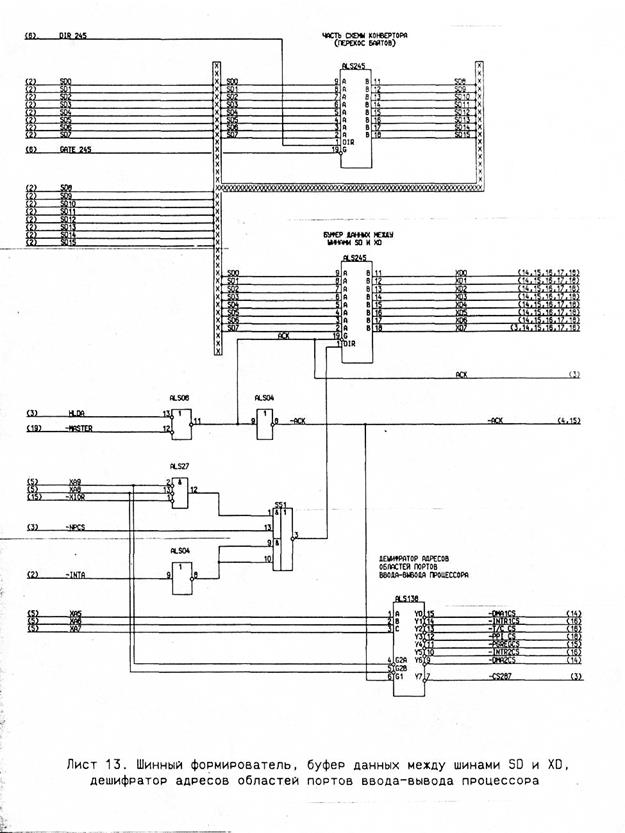

Шинный формирователь, буфер данных между шинами SD

и XD, дешифратор адресов областей портов ввода/выво-

да процессора........................................................................................................... Лист 13.

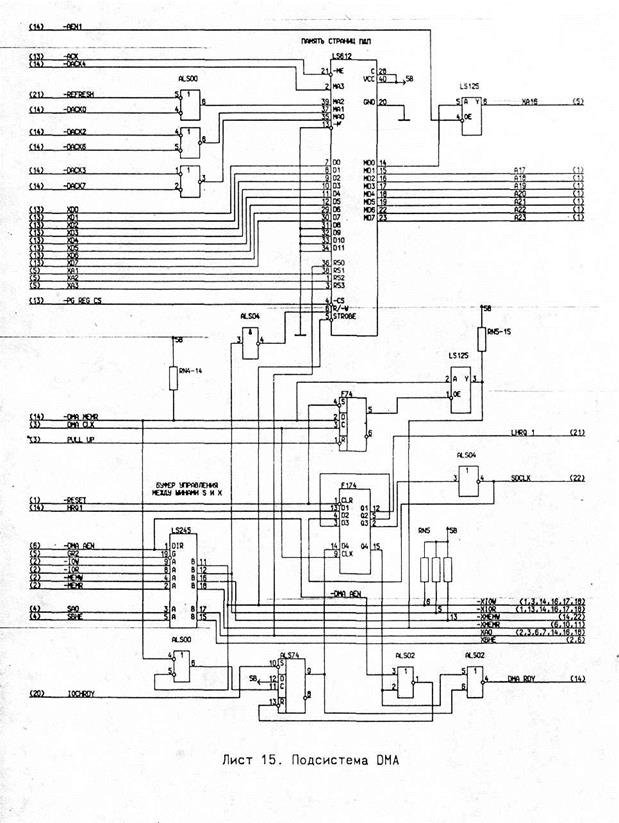

Подсистема DMA (контроллеры DMA)........................................................... Лист 14.

Подсистема DMA (память регистров страниц DMA).................................... Лист 15.

Подсистема прерываний....................................................... ............................... Лист 16.

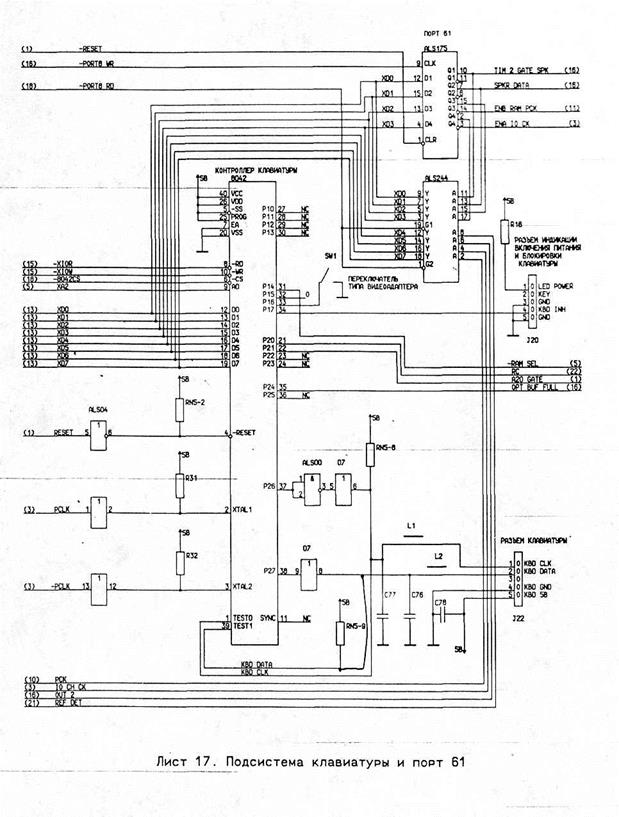

Подсистема клавиатуры и порт 61....................................................................... Лист 17.

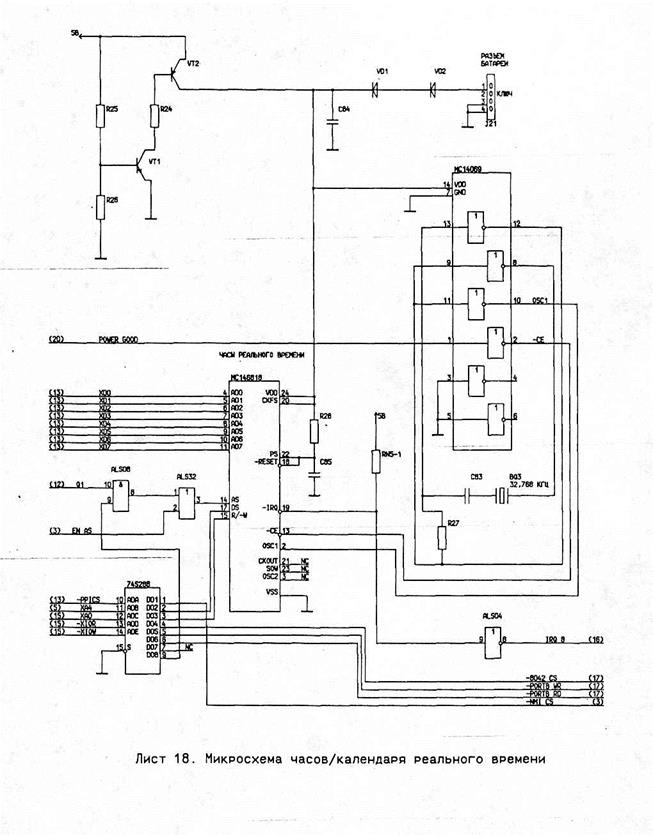

Микросхема часов/календаря реального времени............................................ Лист 18.

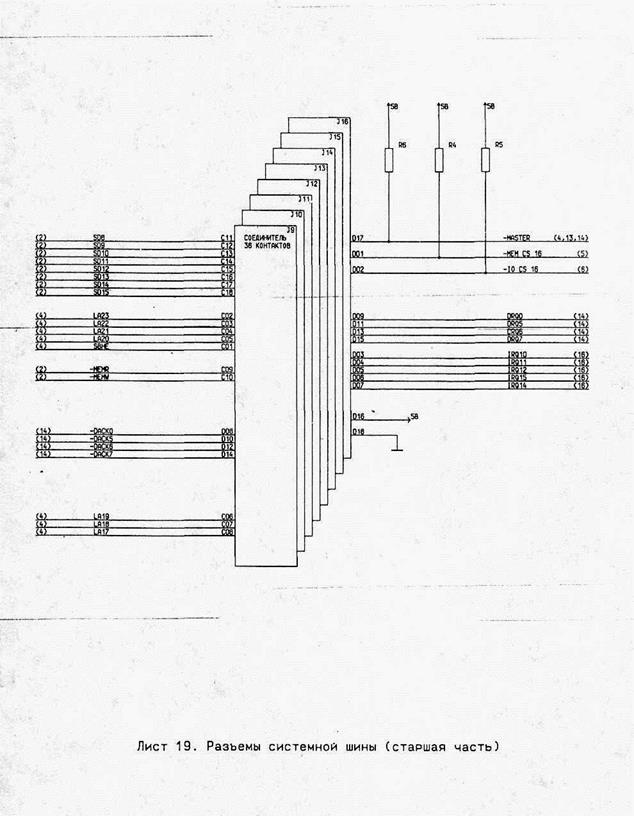

Разъемы системной шины (старшая часть (36 контактов))................................ Лист 19.

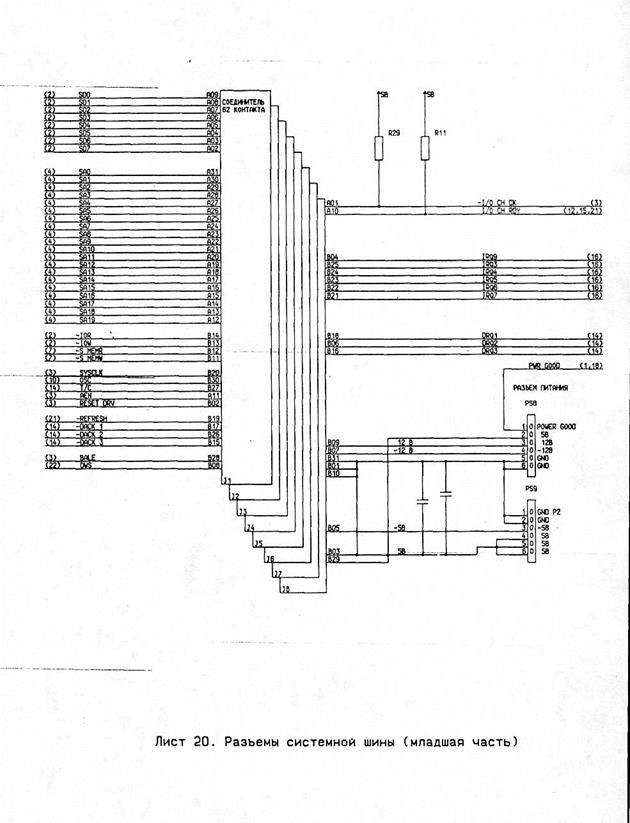

Разъемы системной шины (младшая часть (62 контакта)).... Лист 20.

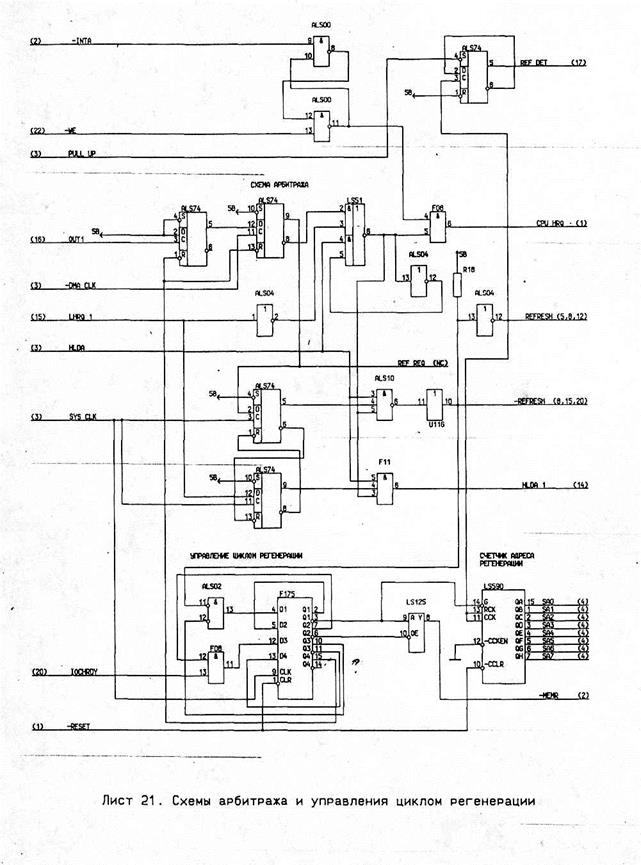

Схемы арбитража и управления циклом регенерации....................................... Лист 21.

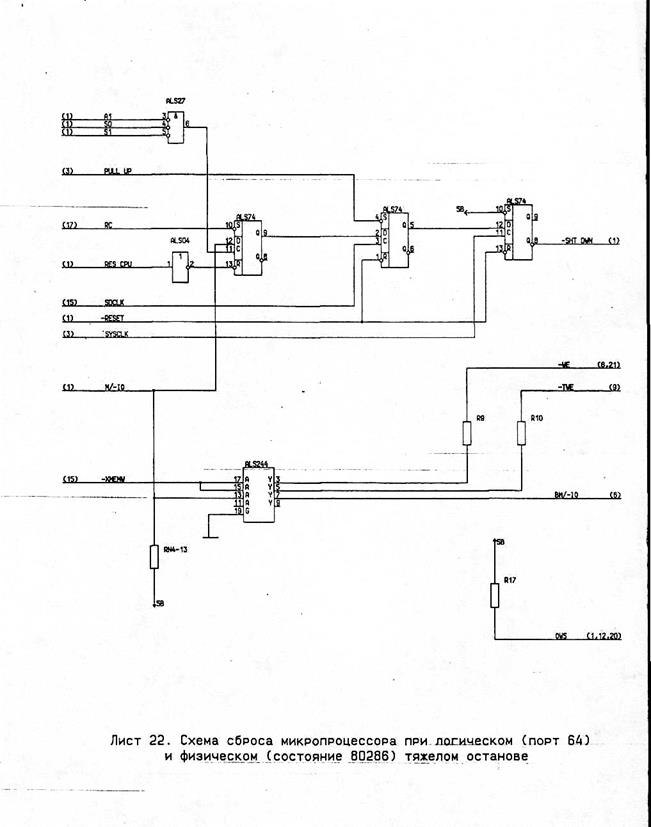

Схема сброса микропроцессора при логическом (порт 64) и

физическом (состояние 80286) тяжелом останове.......................................... Лист 22.

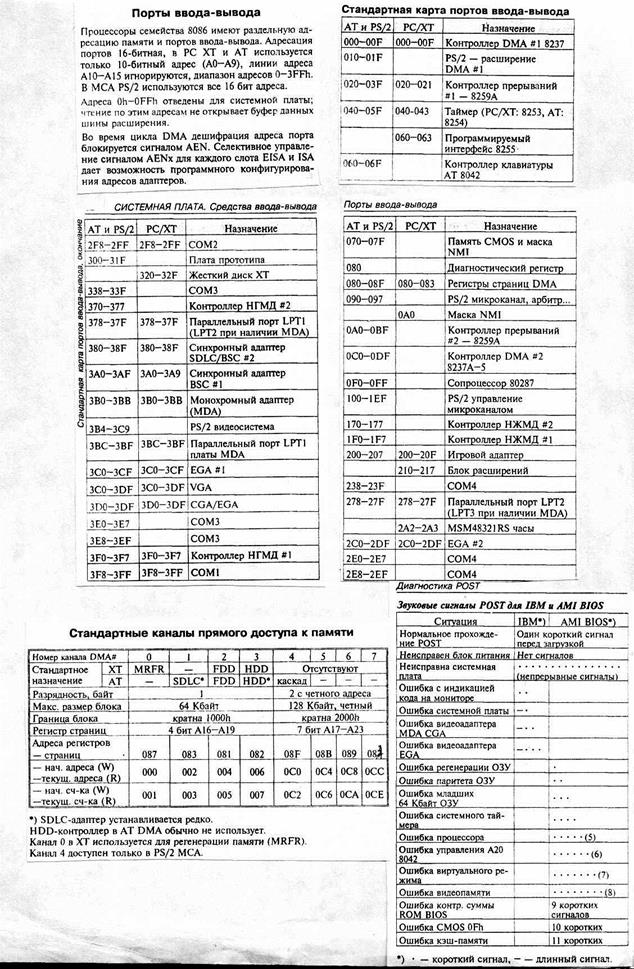

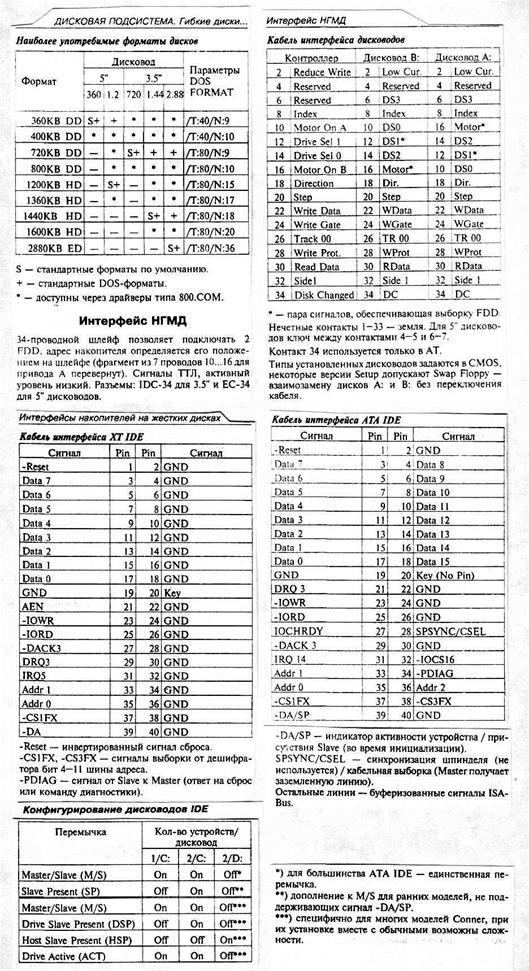

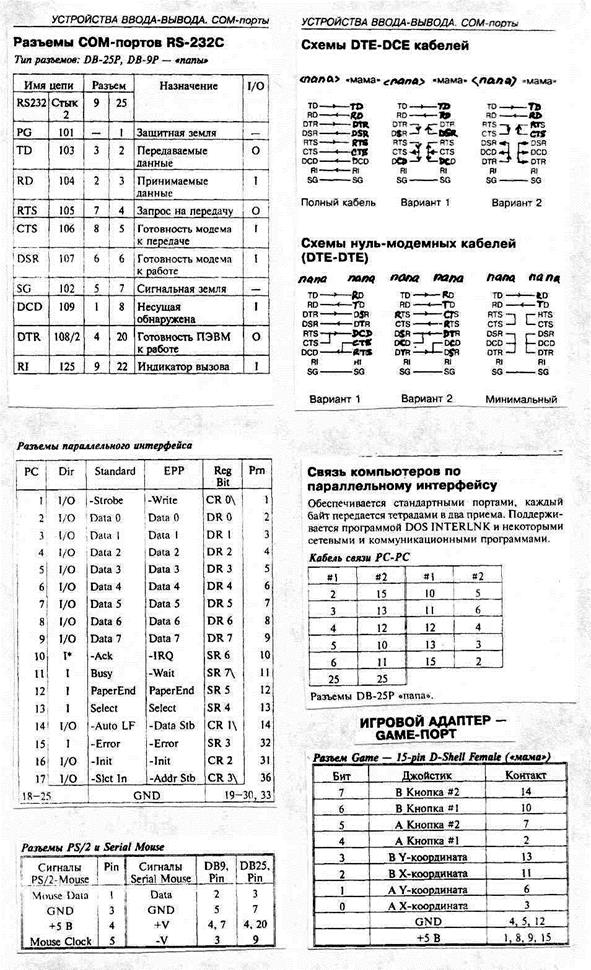

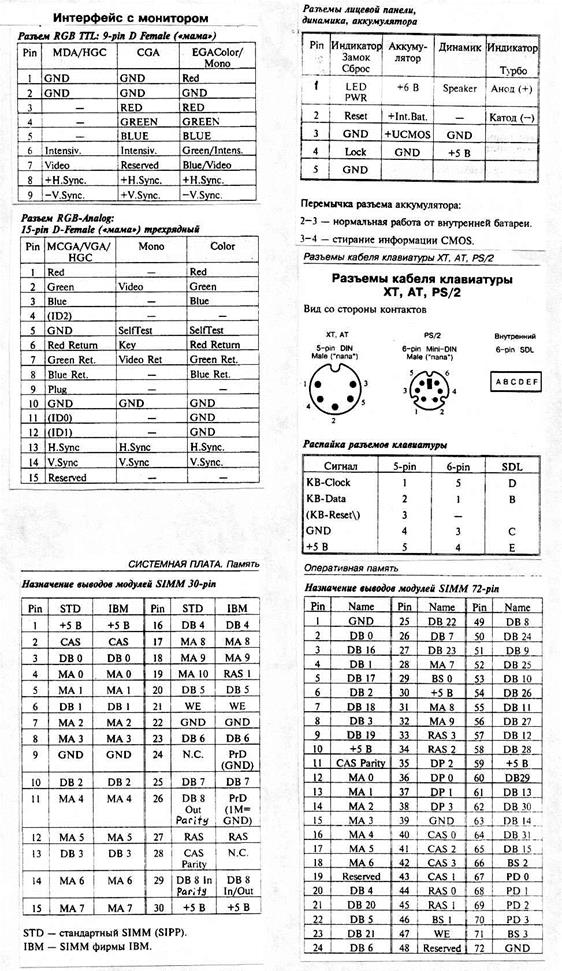

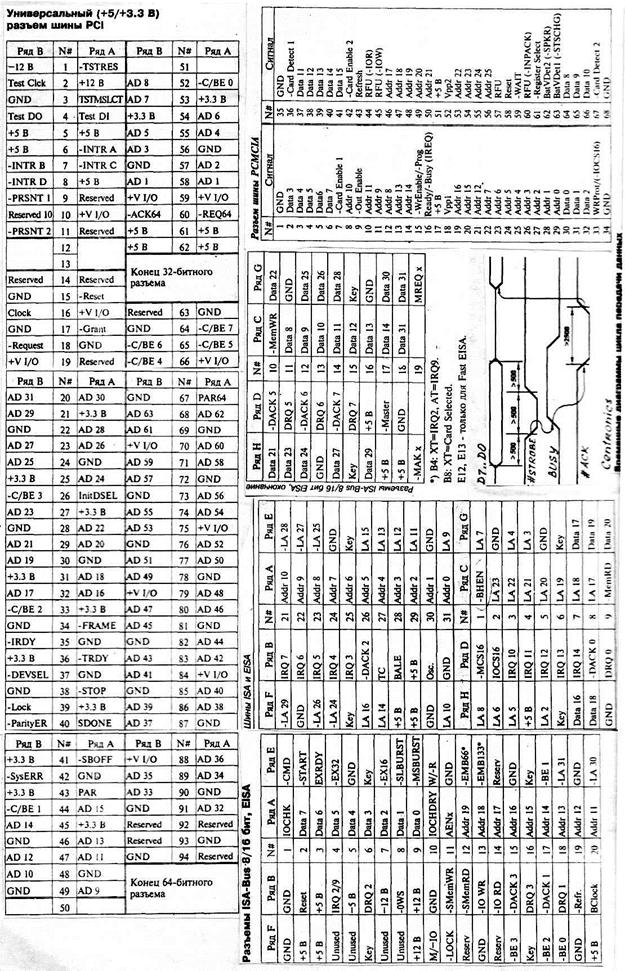

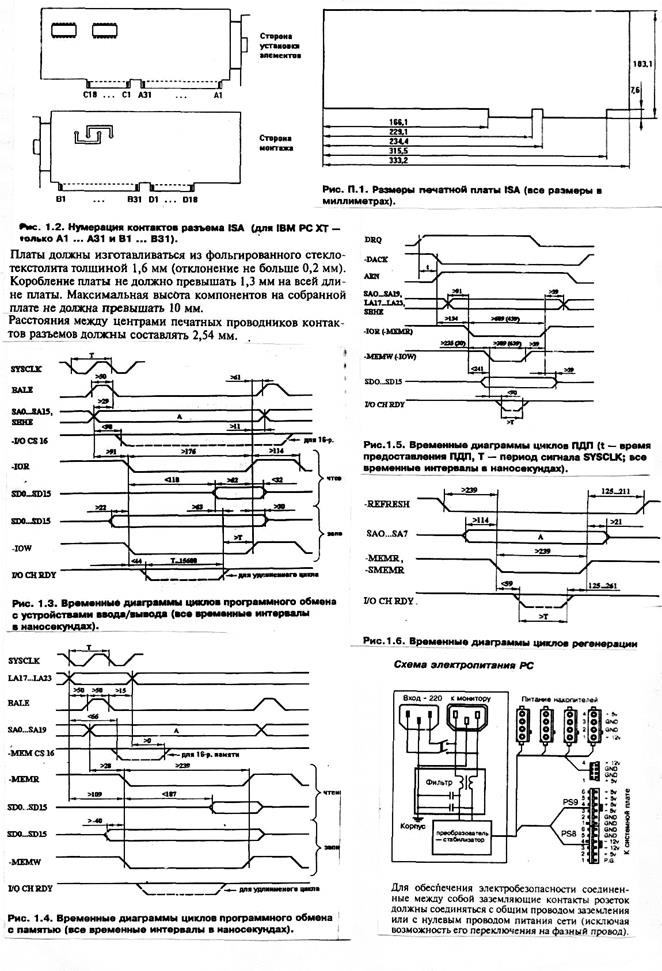

ПРИЛОЖЕНИЯ". Карта портов ввода/вывода, каналов DMA, стандартные звуковые сигналы POST, интерфейсные разъемы.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

© helpiks.su При использовании или копировании материалов прямая ссылка на сайт обязательна.

|