- Автоматизация

- Антропология

- Археология

- Архитектура

- Биология

- Ботаника

- Бухгалтерия

- Военная наука

- Генетика

- География

- Геология

- Демография

- Деревообработка

- Журналистика

- Зоология

- Изобретательство

- Информатика

- Искусство

- История

- Кинематография

- Компьютеризация

- Косметика

- Кулинария

- Культура

- Лексикология

- Лингвистика

- Литература

- Логика

- Маркетинг

- Математика

- Материаловедение

- Медицина

- Менеджмент

- Металлургия

- Метрология

- Механика

- Музыка

- Науковедение

- Образование

- Охрана Труда

- Педагогика

- Полиграфия

- Политология

- Право

- Предпринимательство

- Приборостроение

- Программирование

- Производство

- Промышленность

- Психология

- Радиосвязь

- Религия

- Риторика

- Социология

- Спорт

- Стандартизация

- Статистика

- Строительство

- Технологии

- Торговля

- Транспорт

- Фармакология

- Физика

- Физиология

- Философия

- Финансы

- Химия

- Хозяйство

- Черчение

- Экология

- Экономика

- Электроника

- Электротехника

- Энергетика

Коммутаторы АТМ

9.4.3. Коммутаторы АТМ

Коммутаторы АТМ имеют определенную специфику сравнительно с обычными пакетными коммутаторами, вызванную нерегулярным характером потоков ячеек АТМ и ограниченными функциями их заголовков. Коммутация грунтуется на поиске исходящего порта и его логического канала, которые определяются идентификаторами VPI и VCI исходящих виртуальных тракта и канала, и на сопоставлении их с входным портом и его виртуальным каналом. Поиск порта – пространственная коммутация, обмен логическими каналами – временная, но, в отличие от обычной пространственно-временной коммутации каналов, в коммутаторах АТМ нет установленных временных интервалов, поэтому возможно «состязание» ячеек нескольких логических каналов за один временной интервал. Их конфликт решается буферизацией ячеек. Кроме коммутации и буферизации, коммутатор АТМ может обеспечивать возможности многоадресной передачи и приоритетного обслуживания ячеек. Производительность коммутатора зависит от возможных блокировок при пространственной коммутации и от организации и дисциплины очередей.

Коммутаторы АТМ могут строиться с общей памятью, общей средой или с пространственным разделением.

Коммутаторы с общей памятью.В таком коммутаторе входные и выходные порты (их количество обозначим N) оборудуются собственными контроллерами, непосредственно соединенными с общей памятью, доступной входным контроллерам для записывания и выходным – для считывания. Входной контроллер анализирует заголовок ячейки, определяет, в какую очередь ее поставить, и соответственно информирует процессор коммутатора. Последний в каждом временном цикле должен обработать N входящих ячеек и выбрать N исходящих для дальнейшей передачи, поэтому скорость и записи, и считывания может составлять Nv, где v – скорость обмена через порт. Нужный объем общей памяти определяется числом портов, скоростью обмена и способом ее использования. Память может делиться на N секций, каждая для отдельной упорядоченной очереди, или предусматривать формирование фрагментированных очередей с произвольным расположением, которые описываются связанными списками адресов цепочек фрагментов. В последнем случае нужен меньший объем памяти, а ячейки будут теряться лишь при полном ее заполнении.

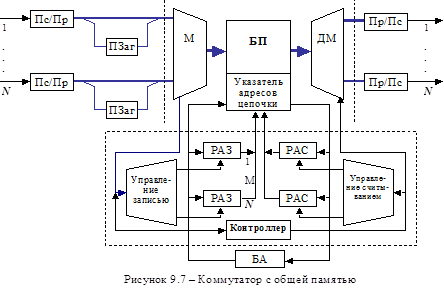

Пример построения коммутатора – на рис. 9.7. Он состоит из:

- входных преобразователей Пс/Пр последовательного кода в параллельный и выходных Пр/Пс для обратного преобразования;

- преобразователей заголовка Пзаг, которые определяют и модифицируют идентификаторы VPI и VCI каждой ячейки;

- блока коммутации, содержащего входной мультиплексор М, буферную память БП и выходной демультиплексор ДМ;

- контроллера, который имеет по паре регистров адресов записи РАЗ и адресов считывания РАС на каждый из N связанных списков;

- буфера адресов БА используемых областей памяти.

Для каждой входной ячейки контроллер определяет связанный список, в который ее следует поместить, с помощью Пзаг соответственно модифицирует ее идентификаторы VCI и VPI и опрашивает нужный РАЗ, откуда получает адрес свободной области памяти, в которую записывается эта ячейка. Одновременно активируется база БА используемых областей памяти, которая выдает адрес новой свободной области, вследствие чего РАЗ и соответствующие указатели адресов цепочки получают новые значения. Аналогично в каждом временном интервале для каждого связанного списка с помощью РАС определяется одна ячейка, извлекаемая из БП и передаваемая в нужный выходной порт с одновременной коррекцией указателей адресов и содержания БА.

Такой коммутатор может обеспечить приоритетное обслуживание ячеек, для чего надо буферизировать ячейки, назначенные определенному выходному порту, в отдельных для каждого уровня приоритета связанных списках. При некоторой модификации коммутатора возможна и многоадресная передача ячеек. После установления виртуального многоадресного соединения в контроллере должна сохраняться соответствующая таблица многоадресной маршрутизации, используемая для записи нужного числа копий каждой ячейки в свои выходные очереди. Для таких ячеек целесообразно иметь отдельный буфер, где они сохраняются, пока нужные копии не будут записаны в надлежащие области БП.

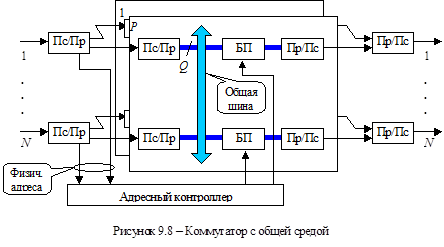

Коммутаторы с общей средой. В таких коммутаторах все входящие ячейки синхронно мультиплексируются в общую среду – скоростную шину или кольцо с временным разделением. Скорость в общей среде должна в N раз превышать скорость входного порта. Каждый выходной порт подключается к шине через адресный фильтр и собственную буферную память БП с упорядоченной очередью FIFO (First-In – First-Out). Адресные фильтры по идентификаторам VPI и VCI заголовков ячеек определяют, следует ли записывать их в свои БП, то есть фактически демультиплексируют общий поток. Вместо отдельных фильтров может использоваться общий адресный контроллер, анализирующий заголовки всех входящих ячеек и определяющий, в какую БП записывать каждую из них рис. 9.8.

При многоадресной передаче ячейка может параллельно заноситься в несколько БП. Для обеспечения нужной скорости предусмотрена параллельная организация данных. Например, входящий битовый поток преобразуется в Р параллельных потоков, каждый из которых со скоростью v/P обрабатывается соответствующей параллельной схемой, где снова превращается в параллельный Q-разрядный код. При необходимости такие коммутаторы могут объединяться в многопортовую многокаскадную схему.

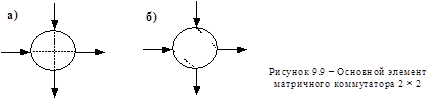

Коммутаторы с пространственным разделением. В них, в отличие от рассмотренных выше коммутаторов, мультиплексирующихь входящую нагрузку в единый поток с скоростью Nv, устанавливаются отдельные соединения и в принципе возможные внутренние блокирования. Коммутаторы с пространственным разделением разделяют на “баньяновые”, матричные, и с N2 отдельными соединениями. В матричных коммутаторах нужно значительно больше коммутационных элементов, а отдельный элемент 2х2 предусматривает два возможных состояния рис. 9.9.

а) сквозное соединение (горизонтальный вход соединен с горизонтальным выходом, вертикальный вход с вертикальным выходом);

б) перекрестное соединение (горизонтальный вход соединен с вертикальным выходом, вертикальный вход с горизонтальным выходом).

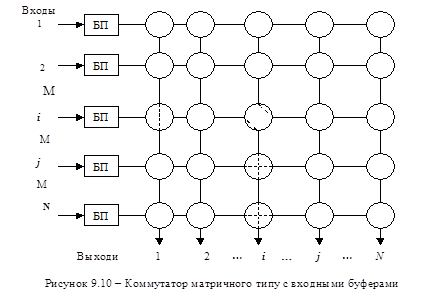

На рис. 9.9 представлен коммутатор матричного типа с входными буферами и пример соединения входа і с выходом j. Для коммутационных элементов, состояние которых на рисунке не показано, оно не имеет значения для данного соединения.

В матричном коммутаторе, как и в “баньяновом”, все нужные переключения коммутационных элементов могут осуществляться индивидуально каждым пакетом, имеющим в заголовке номер выходного порта (т. е. коммутатор является самомаршрутизируемым),

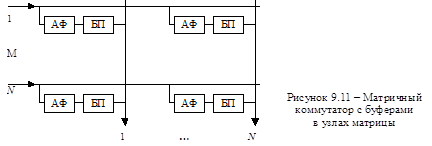

и возможные внутренние блокировки – если в одном временном интервале поступит несколько пакетов, предназначенных определенному выходному порту, то можно передать только один из них, а остальные надо сохранить в буфере, иначе они будут потеряны. Буферные устройства БП могут устанавливаться на входах коммутатора (рис. 9.10) или в узлах коммутационной матрицы (рис. 9.11).

При входных БП функции коммутации и буферизации разделены, что упрощает реализацию соответствующих микросхем. Каждая входная ячейка записывается в БП и, если не может быть передана из-за конфликта, то остается в БП и ожидает следующей попытки. В случае БП с упорядоченной очередью (FIFO) за передачу конкурируют только ячейки, пребывающие в любом БП в начале очереди. Если ячейка не передана из-за внутренней блокировки, она остается в начале очереди и конкурирует за передачу в следующем временном интервале. Ячейки, находящиеся дальше в очереди, тоже блокируются, независимо от номера нужного им выходного порта, что уменьшает пропускную способность такого коммутатора. Для БП с произвольной выборкой усложняется реализация, но заметно возрастает пропускная способность – если начальная ячейка очереди заблокирована, то из очереди выбирается следующая ячейка, порт назначения которой свободен.

В случае расположения БП в узлах коммутационной матрицы функции коммутации и буферизации схемно объединены, что усложняет техническую реализацию, требует большего объема памяти, чем в коммутаторе с входными БП.

В коммутаторе рис. 9.11 адресные фильтры АФ отбирают ячейки для своих выходов. Если в нескольких БП есть ячейки, предназначенные одному выходу, то все они, кроме одной (назовем ее “победителем”), должны быть задержаны. “Победитель” выбирается псевдослучайным или циклическим способом, из самой длинной очереди или из наиболее долго задержанных ячеек. Псевдослучайный и циклический выбор реализуются просто, но, особенно псевдослучайный, ведут к значительным колебаниям длительностей задержки ячеек. Оптимальным для минимизации потерь есть более сложный технически выбор из наиболее длинной очереди, которая грунтуется на механизме сравнения очередей. Оптимальным для минимизации задержек есть выбор из наиболее долго задержанных ячеек, основанный на запоминании порядка поступления конкурирующих ячеек.

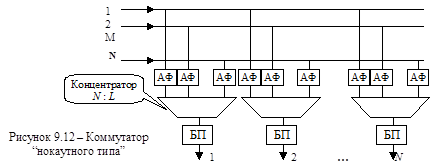

Примером коммутатора с N2 отдельными соединениями есть внутренне неблокированный, так называемый “нокаутный” коммутатор с выходной буферизацией (см. рис. 9.12). В нем каждый входной порт передает ячейки на распределительную шину, к которой подключены все выходные порты. Отдельный выходной порт имеет N адресных фильтров, которые выявляют адресованные ему ячейки, и может параллельно принимать до N ячеек, из которых для занесения в выходную БП с помощью концентратора избирается к L ячеек, а остальные (если такие есть) теряются (по принципу “нокаута”). Для достижения малой вероятности потерь ячеек надлежащим образом избирают параметр L. В частности, при L = 8 эта вероятность не превышает 10-6 практически независимо от нагрузки, а каждое единичное приращение L уменьшает ее почти на порядок.

Укажем, что современные коммутаторы АТМ часто построенные именно по принципу “нокаутa”, в особенности при значительных N.

Типы коммутаторов АТМ.Оборудование АТМ производят несколько десятков известных фирм (New bridge, Fore Systems, Cisco, 3Com и т.п.).В качестве примера реальных возможностей, дальше представлены основные технические характеристики некоторых распространенных типов коммутаторов АТМ.

Коммутатор 36150 MainStreet(фирма New bridge), предназначенный для доступа в сеть АТМ, предусматривает коммутацию виртуальных трактов и каналов на скорости до 12,8 Гбит/с с образованием двопунктових двунаправленных (симметричных или асимметричных) и многопунктовых однонаправленных соединений. Данные о всех соединениях сохраняются в энергонезависимой памяти главного процессора. Коммутатор создан на основе 4-портовой платы с выходными буферами. Коммутатор на 4 порта однокаскадный без внутренних блокировок, на 8 ли 16 портов – многокаскадный с пренебрежимо малыми блокировками. В интерфейсах UNI обеспечивается общее управление потоком GFC с учетом приоритетов для источников с CBR и VBR (AAL первого и пятого типов). Предусмотрены следующие интерфейсы UNI:

- плата Е1 TDM для подключения тракта Е1 с целью транспортирования его сетью АТМ (есть также аналогичная плата для американского стандарта Т1 TDM на 1,5 Мбит/с);

- плата Ethernet для обмена данными между стыком Ethernet (10 Мбит/с) и сетевым интерфейсом АТМ;

- плата Token Ring для обмена данными между стыком Token Ring (4 Мбит/с и 16 Мбит/с) и сетевым интерфейсом АТМ;

- плата FDDI для передачи пакетов FDDI в ячейках АТМ.

- плата NTSC/JPEG для двунаправленной передачи видеосигналов стандарта NTSC с звуком и с возможностью компрессии за стандартом JPEG (без компрессии полоса видеосигнала 127,2, с компрессией программируется на 7,8; 10,2; 12,7; 25,4; 38,2 или 42,4 Мбит/с) (есть также плата РАL/JPEG с аналогичными возможностями, но для видеостандарта РАL).

Возможные сетевые интерфейсы (NNI) коммутатора такие:

ü LATM (Local ATM) – интерфейс ячейкового типа для доступа в сеть АТМ с помощью одно- и многогодовых оптических кабелей на скорости 100 и 140 Мбит/с;

ü STM-1 АТМ (или ОС-3 АТМ) – стык с оборудованием SDH (или SONET) (155 Мбит/с, одноподовый оптический кабель);

ü E3 ATM/PLCP – стык с стандартным цифровым трактом Е3 (34 Мбит/с) с использованием протокола PLCP (Physical Layer Convergence Protocol) конвергенции физического уровня с системами передачи PDH (есть также аналогичный стык для американского стандарта Т3 ATM/PLCP на 45 Мбит/с).

Коммутатор 36170 Mainstreet Xpress (фирма Newbridge) предназначен для транспортной сети АТМ. Предусматривает коммутацию двупунктновых соединений на скорости до 12,8 Гбит/с. Обеспечивает управление нагрузкой для предотвращение перегрузок сети. Строится как дублированная неблокированная полносвязная матрица с выходными буферами. Может иметь до 94 портов STM-1 (ОС-3), до 16 – STM-4 (ОС-12), до 282 – Е3 (Т3) и до 6000 портов Е1 (Т1). Общая пропускная возможность до 102,4 Гбит/с.

Коммутатор ForeRunner ASX-1000(фирма Fore Systems) предназначен для создания транспортной сети АТМ. Предусматривает неблокированную коммутацию с скоростью от 2,5 до 10 Гбит/с. Может иметь от 2 до 96 портов АТМ: STM-1 (ОС-3), STM-4 (ОС-12), Е3 (Т3) на одно и многомодовых оптических кабелях.

[1] Ресурсы сети используются эффективно, поскольку доступные всем службам и могут оптимально распределятся между ними на статистической основе.

[2] Гибкость сети определяется тем, что каждый источник может генерировать информацию с необходимой ему скоростью, поэтому возможно постоянно усовершенствовать алгоритмы кодирования и сжатия информации для уменьшения необходимой полосы пропускания и внедрять новые информационные службы с еще неизвестными характеристиками.

[3] Ймовірність втрати комірки в комутаторі обмежена діапазоном 10-8…10-10.

[4] Ячейки, що генерированные пользователем (application) услуг уровня АТМ, но не переносящие информации этого пользователя.

[5] Потоки данных техэксплуатации нумеруются по уровням виртуального соединения– от F1 для уровня регенерационной секции до F5 для уровня виртуального канала.

|

|

|

© helpiks.su При использовании или копировании материалов прямая ссылка на сайт обязательна.

|