- Автоматизация

- Антропология

- Археология

- Архитектура

- Биология

- Ботаника

- Бухгалтерия

- Военная наука

- Генетика

- География

- Геология

- Демография

- Деревообработка

- Журналистика

- Зоология

- Изобретательство

- Информатика

- Искусство

- История

- Кинематография

- Компьютеризация

- Косметика

- Кулинария

- Культура

- Лексикология

- Лингвистика

- Литература

- Логика

- Маркетинг

- Математика

- Материаловедение

- Медицина

- Менеджмент

- Металлургия

- Метрология

- Механика

- Музыка

- Науковедение

- Образование

- Охрана Труда

- Педагогика

- Полиграфия

- Политология

- Право

- Предпринимательство

- Приборостроение

- Программирование

- Производство

- Промышленность

- Психология

- Радиосвязь

- Религия

- Риторика

- Социология

- Спорт

- Стандартизация

- Статистика

- Строительство

- Технологии

- Торговля

- Транспорт

- Фармакология

- Физика

- Физиология

- Философия

- Финансы

- Химия

- Хозяйство

- Черчение

- Экология

- Экономика

- Электроника

- Электротехника

- Энергетика

МIНIСТЭРСТВА АДУКАЦЫI РЭСПУБЛIКI БЕЛАРУСЬ

МИНИСТЕРСТВО СВЯЗИ И ИНФОРМАТИЗАЦИИ РЕСПУБЛИКИ БЕЛАРУСЬ

ВИТЕБСКИЙ ФИЛИАЛ

Учреждение образования

«ВЫСШИЙ ГОСУДАРСТВЕННЫЙ КОЛЛЕДЖ СВЯЗИ»

КАФЕДРА ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ СЕТЕЙ ТЕЛЕКОММУНИКАЦИИ

Устройство СУММИРОВАНИЯ двоичных чисел

Пояснительная записка

к курсовому проекту

по дисциплине

«ЦИФРОВЫЕ И МИКРОПРОЦЕССОРНЫЕ УСТРОЙСТВА»

| Выполнил учащийся гр. ТЭ 252 | В.А.Николаечкина | |

| Руководитель – преподаватель | О. Д. Цыбульская | |

Витебск 2014

МIНIСТЭРСТВА АДУКАЦЫI РЭСПУБЛIКI БЕЛАРУСЬ

ВIЦЕБСКI ФIЛIЯЛ УА «ВДКС»

(назва установы адукацыi)

ЗАЦВЯРДЖАЮ

Зав. фiл. кафедры ПОСТ В.В.Сементовская

« _____ » ________2014 г.

ЗАДАННЕ

на курсавы праект ( работу )

Навучэнцу Николаечкина Виолетта Александровна _________________

(прозвiщча, iмя, iмя па бацьку)

Курса 5 групы ТЭ 252

па дысцыплiне Цифровые и микропроцессорные устройства Тема курсавога праекта ( работы ) Устройство суммирования двоичных чисел

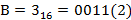

Зыходныя данныя Вариант 4 А= D В= 3 Тип логики – КМОП ___________

______ Ксч=14 ___

__________________________________Базис – И-НЕ_____________________________________

________________________________Регистр сдвига влево________________________________

Склад праекта ( работы )

Тлумачальная запiска

Змест раздзелау Тэрмiн выканання

Введение 15.09.2014 1 Описательный раздел 17.09.2014 2 Расчетный раздел 18.09.2014 3 Конструктивный раздел 19.09.2014

Графiчная частка праекта

Лiст - 1 Схема электрическая структурная 15.09.2014 Лiст – 2 Схема электрическая принципиальная 20.09.2014

Дата выдачы “ 15 ” сентября 2014 г.

Тэрмiн заканчэння “ 20 ” сентября 2014 г.

Выкладчык-кiраунiк

курсавога праекта О. Д. Цыбульская

Подпiс навучэнца _________________ В. А. Николаечкина

СОДЕРЖАНИЕ

Введение 4 1.Описательный раздел 5 1.1 Постановка задачи 5 1.2 Краткое техническое описание 5-6 2. Расчетный раздел 7 2.1 Сложение чисел А и В 7

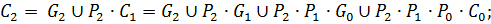

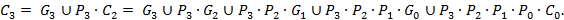

2.2 Синтез счётчика 7-13

2.3 Синтез регистра 13-16

2.4 Выбор сумматора 16-17

2.5 Синтез четырехразрядного параллельного сумматора 17-22

2.6 Синтез регистра 22-24

2.7 Выбор триггера переноса 24

3. Конструктивный раздел 25-26

4. Графический раздел 27

4.1 Схема электрическая структурная 27(1)

4.2 Схема электрическая принципиальная 27(2)

Заключение 28

Литература 29

ВВЕДЕНИЕ

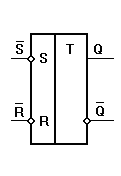

RS-триггер – это триггер с установочными входами.

RS-триггер – это триггер с установочными входами.

Рисунок 1 - Условное графическое обозначение RS – триггера

Вход S – предназначен для установки триггера в «1» состояние (Q = 1) при подаче на него активного сигнала. Вход R – предназначен для установки триггера в «0» состояние (Q = 0) при подаче на него активного сигнала. RS-триггеры могут быть асинхронными и синхронными. В асинхронных триггерах состояние на выходе изменяется в момент поступления сигналов на информационные входы. В синхронных триггерах для передачи сигнала с информационных входов на выход требуется специальный синхронизирующий импульс. Синхронные триггеры подразделяются на триггеры со статическим управлением и триггеры с динамическим управлением. В триггерах с динамическим управлением передача сигналов с информационных входов на выходы осуществляется либо по фронту синхронизирующего импульса, либо по спаду синхронизирующего импульса.

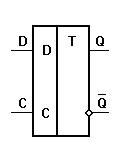

D-триггер – это триггер с задержкой.

D-триггер – это триггер с задержкой.

Рисунок 2 - Условное графическое обозначение D – триггера

Является всегда синхронным. Он переходит в то состояние, которое соответствует логическому сигналу на входе D. При этом сигнал на выходе триггера появляется только после того, как закончится действие синхроимпульса. Передача информации с входа D на выход Q осуществляется во время действия синхронизирующего импульса. Широко используют D-триггеры с динамическим управлением. В них передача информации с информационных ходов на выходы осуществляется либо по фронту синхронизирующего импульса, либо по спаду синхронизирующего импульса.

1. ОПИСАТЕЛЬНЫЙ РАЗДЕЛ

1.1 Постановка задачи

Разработать принципиальную электрическую схему устройства суммирования двоичных чисел с параллельным переносом в соответствии с заданной структурной схемой (Лист 1) на микросхемах схемотехники КМОП.

Описать принцип построения и разработать в базисе «И-НЕ» логическую схему четырехразрядного двоичного сумматора с параллельным переносом.

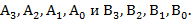

Предусмотреть ввод четырехразрядного слагаемого А и четырехразрядного слагаемого В. Для ввода числа А использовать счетчик (Y1), а для ввода числа В – регистр (Y2). Выполнить сложение чисел А и В, заданных в двоичной системе счисления, обозначить разряды слагаемых как

Выполнить полный синтез четырехразрядного двоичного сумматора (Y3) для значения чисел А=D и В=3, заданных в шестнадцатеричной системе счисления.

Выбрать регистр (Y4), который используется для вывода результата сложения двух заданных чисел без учета переноса.

Осуществляется выбор триггера переноса (Y5), который служит для учета переноса, возникающего в результате сложения чисел А и В.

1.2 Краткое техническое описание

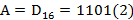

Все цифровые устройства выполняют действия над величинами представленными в двоичной системе счисления, поэтому слагаемое А=D и слагаемое В=3 должны быть преобразованы из шестнадцатеричной системы счисления в двоичную.

Преобразование числа А выполняет счетчик (Y1), выполненный на микросхемах DD1,2 типа К561ЛА7, DD3 типа К561ЛА9, DD4,5 типа К561ИЕ11.

Для преобразования числа В используют регистр (Y2), выполненный на микросхемах DD6,7 типа К564ТВ1.

В результате такого преобразования был получен двоичный код числа А=1101(2) и В=0011(2). Для того чтобы сложить два слагаемых в проекте использован четырехразрядный сумматор (Y3). Выполненный на микросхемах DD8,9,10,11,12,14 типа К561ЛА7, DD13 типа К561ЛА9, DD15,16,17,18 типа К561ИМ1.

Результат сложения без учета переноса выдается регистром (Y4), который построен на микросхемах DD19,20 типа К564ТВ1.

Перенос, полученный при сложении чисел А и В выдается триггером переноса, который выполнен на микросхемах DD21 типа К561ТВ1.

2. РАСЧЕТНЫЙ РАЗДЕЛ

2.1 Сложение чисел А и В

Разберем процесс сложения двоичных чисел А= D и В=3, заданных в шестнадцатеричной системе счисления. Для этого представим эти числа в двоичной системе.

Обозначим разряды слагаемых.

Выполним сложение чисел.

+

10000

В результате сложения заданных чисел получается перенос в пятый разряд. Таким образом полный результат сложения А + В = 10(16). Запишем в принятых обозначениях.

2.2 Синтез счетчика

Счетчик в устройстве суммирования двоичных чисел нужен для того, чтобы двоичным кодом представить число А равно D(16).

Числа в счетчике представляются определенными комбинациями состояний триггеров, при поступлении на вход очередного импульса, в суммирующем счетчике установится новая комбинация, соответствующая числу, которое на 1 больше предыдущего числа.

Составим таблицу работы счетчика с Ксч = 14 в базисе «И-НЕ» для числа А = 1101(2).

Таблица 1 – Таблица работы счетчика

| № входа импульса | Предыдущее состояние | Следующее состояние | ||||||

|

|

|

|

|

|

|

| |

Сопоставим таблицу переходов для JK – триггера.

Таблица 2 – Таблица переходов

| Вид перехода | J | K |

| - | |

| - | |

| - | |

| - |

Составим таблицу переключений триггеров счетчика.

Таблица 3 – Таблица переключений

| № вход. имп-ов |

|

|

|

|

|

|

|

|

|

|

|

|

| - |

| - |

| - |

| - | |||||

| - |

| - |

| - |

| - | |||||

| - |

| - |

| - |

| - | |||||

| - |

| - |

| - |

| - | |||||

| - |

| - |

| - |

| - | |||||

| - |

| - |

| - |

| - | |||||

| - |

| - |

| - |

| - | |||||

| - |

| - |

| - |

| - | |||||

| - |

| - |

| - |

| - | |||||

| - |

| - |

| - |

| - | |||||

| - |

| - |

| - |

| - | |||||

| - |

| - |

| - |

| - | |||||

| - |

| - |

| - |

| - | |||||

| - |

| - |

| - |

| - |

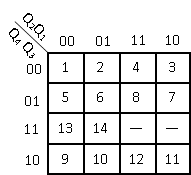

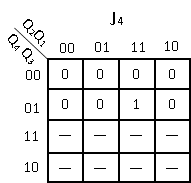

Для того чтобы записать логические выражения для входов триггеров, составляем шаблон карты Карно.

Рисунок 3 – Шаблон карты Карно

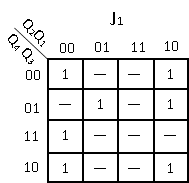

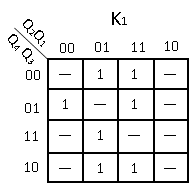

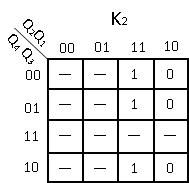

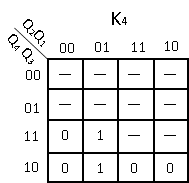

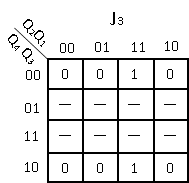

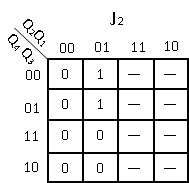

По заданному шаблону составим карты Карно для каждого входа всех триггеров.

Рисунок 4 – Карты Карно

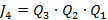

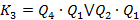

Запишем логические выражения.

Переведем полученные выражения в базис «И-НЕ».

Построим счетчик в базисе «И-НЕ» для  = 14.

= 14.

| J1 |

| K1 |

| C1 |

| J2 |

| K2 |

| C2 |

| J3 |

| K3 |

| C3 |

| R3 |

| J4 |

| K4 |

| C4 |

| & |

| & |

| & |

| & |

| & |

| & |

| & |

| & |

| & |

| & |

| & |

| & |

| & |

| «1» |

| «1» |

| т1 |

| т2 |

| т3 |

| т4 |

| DD4.1 |

| DD4.2 |

| Вход синхронизации |

| Q1 |

| Q1 |

| R2 |

| DD2.2 |

| DD2.3 |

| DD1.4 |

| DD5.1 |

| Q2 |

| Q3 |

| Q1 |

| Q2 |

| Q3 |

| Q4 |

| Q2 |

| Q4 |

| DD3.1 |

| DD3.2 |

| Q4 |

| R4 |

| Сброс |

| R1 |

| Q4 |

| DD3.3 |

| DD2.1 |

| Q3 |

| Q2 |

| DD5.2 |

| DD2.4 |

| DD1.3 |

| DD1.2 |

| DD1.1 |

Рисунок 5 – Схема счетчика с Ксч = 14

Выберем логические элементы:

DD1К561ЛА7;

DD2К561ЛА7;

DD3К561ЛА9;

DD4К561ИЕ11;

DD5К561ИЕ11;

2.3 Синтез регистра

Для формирования числа В=1101(2) согласно заданию был использован регистр (Y2) построенный на основе D-триггера. Из предложенного набора микросхем серии К561 выбираем триггер К561ТМ2.

Условно графическое обозначение D-триггера приведено на рисунке 6.

К561ТМ2

| S1 |

| D1 |

| D2 |

| S2 |

| C1 |

| C2 |

| R1 |

| R2 |

| Q1 |

| Q1 |

| Q2 |

| Q2 |

| T1 |

| T2 |

Рисунок 6 – Условно графическое обозначение D-триггера

Назначение выводов микросхем:

1,13 – прямые выходы;

2,12 – инверсные выходы;

3,11 – выходы синхронизации;

4,6,8,10 – установочные входы;

5,9 – информационные входы;

7 – общий;

14 – питание.

Микросхема К561ТМ2 содержит два двухтактных D-триггера. По фронту первого импульса на входе логический уровень присутствует на входе D, записывается в первый однотактный D-триггер. По фронту два импульса синхронизируемый на выходе Q устанавливают уровень, который присутствовал на входе D перед первым синхроимпульсом. Таким образом на выходе двухтактного D-триггера сигнал задерживается на один такт.

Входы R и S не зависят от импульсов синхронизации и имеют активные высокие уровни.

Составим таблицу работы регистра В=1101(2). Регистр осуществляет сдвиг влево.

Таблица 4 – Таблица работы регистра

| С |

|

|

|

| Режим работы |

| - | Ø | Ø | Ø | Ø | Исходное состояние |

| Ø | Ø | Ø | Режим записи | ||

| 1 | |||||

| Режим считывания | |||||

| Ø | Ø | ||||

| Ø | Ø | Ø | |||

| Ø | Ø | Ø | Ø |

Построим регистр на основе D-триггера серии К561.

| Вход синхронизации |

| S1 |

| S2 |

| S3 |

| S4 |

| D1 |

| R1 |

| C1 |

| D2 |

| D3 |

| D4 |

| C2 |

| C3 |

| C4 |

| R2 |

| R3 |

| R4 |

| Т1 |

| Т2 |

| Т3 |

| Т4 |

| Вход |

| Q1 |

| Q1 |

| Q4 |

| DD6.1 |

| DD6.2 |

| DD7.1 |

| DD7.2 |

| Q2 |

| Q2 |

| Q3 |

| Q3 |

| Q4 |

| Сброс |

Рисунок 7 – Регистр со сдвигом влево

Выбираем элементы микросхемы:

DD6Л564ТВ1;

DD7К564ТВ1.

2.4 Выбор сумматора

Условно графическое изображение сумматора изображено на рисунке 8.

К561ИМ1

| А1 |

| А2 |

| А3 |

| А4 |

| В1 |

| В2 |

| В3 |

| В4 |

| Рс |

| S1 |

| S2 |

| S3 |

| S4 |

| P |

| 5 |

| 3 |

| 1 |

Рисунок 8 – Условно графическое изображение сумматора

Назначение выводов микросхемы:

1,3,5,7 – коды первого числа;

2,4,6,15 – коды второго числа;

8 – общий;

9 – вход сигнала ускоренного переноса;

10,11,12,13 – выход сигнала ускоренного переноса;

14 – выход сигнала ускоренного переноса;

16 – питание.

Микросхема К561ИМ1 содержит четырехразрядный сумматор с устройством ускоренного переноса, такая структура повышает быстродействие многоразрядных арифметических узлов, состоящих из нескольких сумматоров.

2.5 Синтез четырехразрядного параллельного сумматора

Сумматоры предназначены для выполнения арифметических операций сложения и вычитания, как двоичных, так и десятичных чисел. По виду выполнения операций можно выделить две группы сумматоров:

- сумматоры, выполняющие сложение положительных чисел (без учета знака);

- сумматоры, выполняющие операцию сложения положительных и отрицательных чисел.

По используемой системе счисления сумматор, который используется в курсовом проекте, является двоичным, то есть выполняет операции над двоичными числами.

По последовательности выполнения операции сумматоры бывают:

- параллельные сумматоры, в которых все разряды складываемых чисел подаются одновременно. Такие сумматоры строятся на комбинационных устройствах;

- последовательные сумматоры, на входы которых, разряды складываемых чисел подаются последовательно во времени, то есть разряд за разрядом. В них используются элементы памяти.

Среди двоичных сумматоров различают: одноразрядные и многоразрядные. Одноразрядные служат основой построения многоразрядных. Многоразрядные сумматоры подразделяются на сумматоры с последовательным и параллельным переносом.

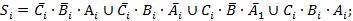

Четырехразрядный двоичный сумматор с параллельным переносом (Y3), предназначенный для сложения четырехразрядных двоичных чисел А и В, представленных разрядами  На выходе сумматора формируется четырехразрядная сумма S, представленная разрядами

На выходе сумматора формируется четырехразрядная сумма S, представленная разрядами  а так же перенос Р.

а так же перенос Р.

Работа устройства синхронизируется тактовыми импульсами  , причем ввод слагаемых осуществляется по отрицательному перепаду сигнала синхронизации, а вывод результата по положительному перепаду.

, причем ввод слагаемых осуществляется по отрицательному перепаду сигнала синхронизации, а вывод результата по положительному перепаду.

Процесс функционирования устройства поясняется временной диаграммой, которая представлена на рисунке 9.

| Тс |

| Uс |

| t1 |

| t2 |

| t3 |

| t4 |

| t |

Рисунок 9 – Временная диаграмма, поясняющая процесс функционирования устройства

В момент времени t, по отрицательному перепаду тактового импульса  , начинается ввод слагаемых. К моменту времени

, начинается ввод слагаемых. К моменту времени  , ввод заканчивается и начинается сложение. К моменту времени

, ввод заканчивается и начинается сложение. К моменту времени  , результат сложения записывается в регистр (Y4) и триггер переноса (Y5).

, результат сложения записывается в регистр (Y4) и триггер переноса (Y5).

Сложение многоразрядных двоичных чисел производится путем их поразрядного сложения с переносом между разрядами.

Полные одноразрядные сумматоры используются в многоразрядных сумматорах, при сложении разрядов двоичных чисел начиная с первого.

Поэтому основным узлом многоразрядных сумматоров является одноразрядный сумматор, который выполняет арифметические сложения одноразрядных двоичных чисел  и перенос из младшего разряда

и перенос из младшего разряда  . В результате на выходах образуется сумма S, и перенос в старший разряд

. В результате на выходах образуется сумма S, и перенос в старший разряд  . В таблице 5 приведена работа одноразрядного сумматора.

. В таблице 5 приведена работа одноразрядного сумматора.

Таблица 5 – Таблица истинности одноразрядного сумматора

| Входы | Выходы | ||||

|

|

|

|

| |

Продолжение таблицы 5.

| 1 | 1 | 1 | 1 | 1 |

Как видно из таблицы 5 при  полный сумматор выполняет функции полусумматора. Логические функции для выводов

полный сумматор выполняет функции полусумматора. Логические функции для выводов  и

и  одноразрядного сумматора, записанные в совершенной нормальной дизъюнктивной форме по данным таблицы 5 имеют вид:

одноразрядного сумматора, записанные в совершенной нормальной дизъюнктивной форме по данным таблицы 5 имеют вид:

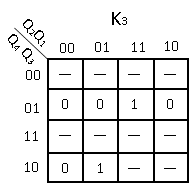

Карта Карно минимизации выражения переноса  выглядит следующим образом, как представлено на рисунке 10.

выглядит следующим образом, как представлено на рисунке 10.

| Вi |

| Ai |

| Ci |

| 01 |

| 11 |

| 0 |

| 0 |

| 1 |

Рисунок 10 – Карта Карно для

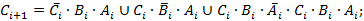

В результате минимизации логическое выражение для переноса  записывается в виде:

записывается в виде:

Применив теорему Моргана, выходной сигнал переноса будет выглядеть следующим образом:

Многоразрядные двоичные сумматоры выполняют операцию сложения двух оперантов, каждый из которых представляет собой n – разрядное двоичное число.

Полученные выражения свидетельствуют от том, что для получения сигналов переноса  достаточно располагать функциям

достаточно располагать функциям

и сигнала внешнего переноса

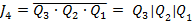

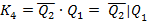

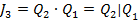

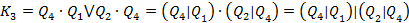

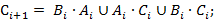

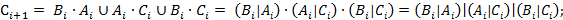

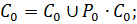

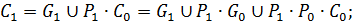

и сигнала внешнего переноса  . Они описывают двухступенчатые комбинационные устройства в первой ступени, которые формируют логические произведения, а во второй – логические суммы. Рассмотренный способ формирования переносов называется параллельным, а сумматоры, построенные по этому способу – сумматорами с параллельным переносом. Перевод полученных выражений в базисе «И-НЕ» дает выражения:

. Они описывают двухступенчатые комбинационные устройства в первой ступени, которые формируют логические произведения, а во второй – логические суммы. Рассмотренный способ формирования переносов называется параллельным, а сумматоры, построенные по этому способу – сумматорами с параллельным переносом. Перевод полученных выражений в базисе «И-НЕ» дает выражения: