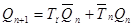

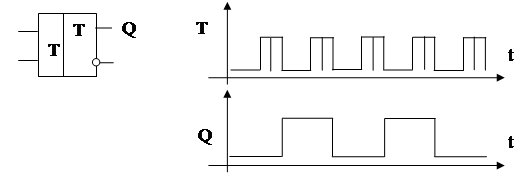

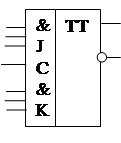

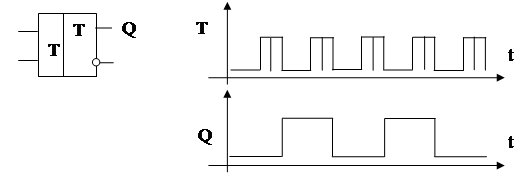

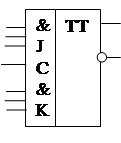

Асинхронный Т триггер

Асинхронный Т триггер

Если соединить JK, то получиться Т.

Переходные процессы. Гонки (RACES).

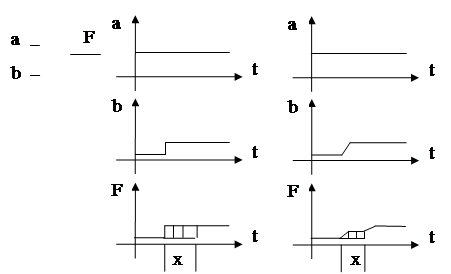

Задержка схемы складываются из задержек срабатывания логических элементов и задержек распределения сигнала по дорожкам платы. Последние пока учитывают только для схем на ЭСЛ. В некоторых схемах не учет задержек приводит к неправильной работе этой схемы с учетом задержек обнаруживаем на выходе импульс, помехи с длительностью близкой к tзд.р. инвертора. Линии со стрелками показывают причинно-следственные связи в цепочке переключений.

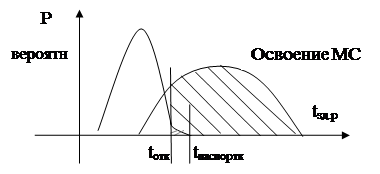

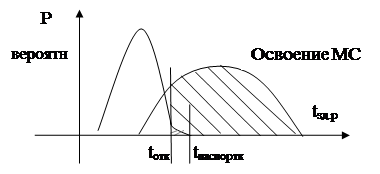

На заводе изготовителе микросхем есть выходной контроль продукции, где отбраковывают НМС, у которых задержка распространения превышает допуск. Можно предположить, что микросхемы с задержкой, меньшей в 8 раз чем максимально допустимая, никогда не встретятся, но заводы изготовители такую гарантию не дают. Поэтому обычно считают, что задержка ЛЭ может быть от нуля до tзд.р. max и изготавливают это: На заводе изготовителе микросхем есть выходной контроль продукции, где отбраковывают НМС, у которых задержка распространения превышает допуск. Можно предположить, что микросхемы с задержкой, меньшей в 8 раз чем максимально допустимая, никогда не встретятся, но заводы изготовители такую гарантию не дают. Поэтому обычно считают, что задержка ЛЭ может быть от нуля до tзд.р. max и изготавливают это:

Здесь Х – переходный процесс, или время неопределенности. Второй рис наглядный, но может быть спутан с изображением 2 сост.

Гонки (состязания фронтов) бывают на участках схем, где сигнал разветвляется и получившееся два сигнала распространяются по двум независимым цепочкам элементов, а затем оба сигнала «встречаются» на входах одного элемента. Из-за различия сумм задержек в этих цепочках на выходе схемы могут появляться импульсы помехи фронта.

Есть 3 способа борьбы с гонками:

1. Построение противогоночных схем, напр. а) при появлении в одной цепочке он запирает вторую цепочку; б) в месте встречи фронтов от двух цепочек ставят ИЛИ, через которую просто раньше проходит тот фронт, что пришел первым, т.е. помеха не возникает;

2. Учет минимального времени задержки, которое хотя нигде и не оговорено, но если одна цепочка состоит из числа N ЛЭ, которое больше числа М элементов другой цепочки, например в 8 раз (N≥М);

3. Введение синхронизации (тактирования) – является самым универсальным при этом ко всем узлам устройства подводят один из двух синхрос C1 C2 в цепочка поочередно. Интервалы между C1 C2 заведомо больше чем максимальная задержка в узлах между ними. Поэтому большинство NC последовательных устройств делают синхронными. Гонки по входу см D трат

Сигналы на выходах R, S являются разрешающими, подготовительными, а сигнал на входе С – исполнительный, по которому происходит переключение триггера С – CLOCK – часы, иногда L – LOAD – загрузка, иногда H- HOLD – захват, удержание.

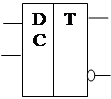

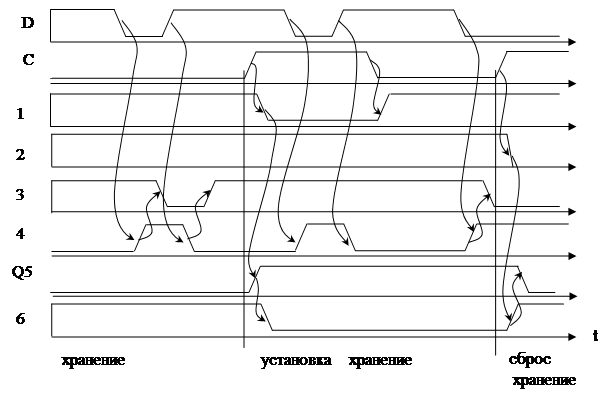

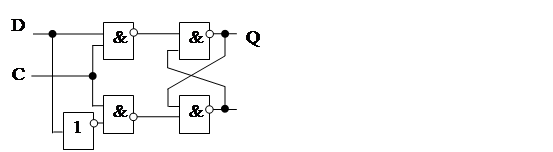

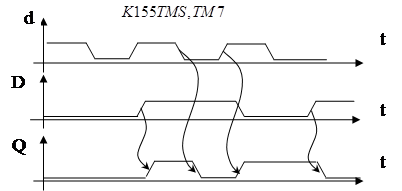

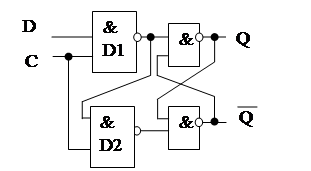

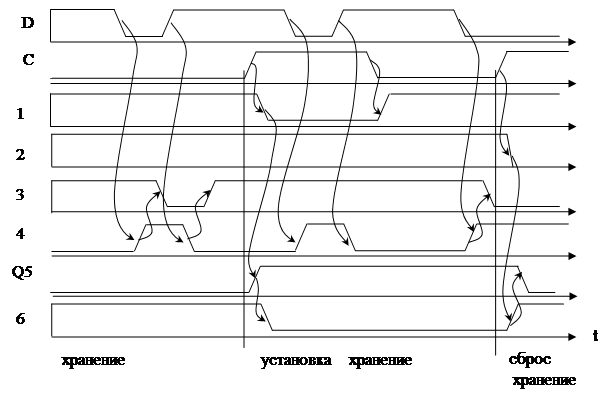

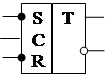

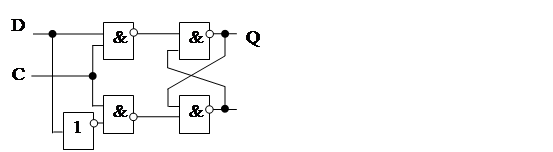

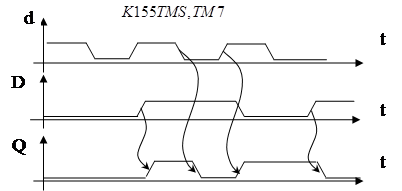

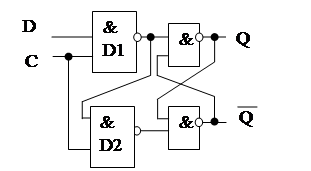

Синхронный D триггер со статическим управлением. LATCH – прозрачная защелка.

Выход Q такого D триггера по сигналу на C входе принимает то же Выход Q такого D триггера по сигналу на C входе принимает то же

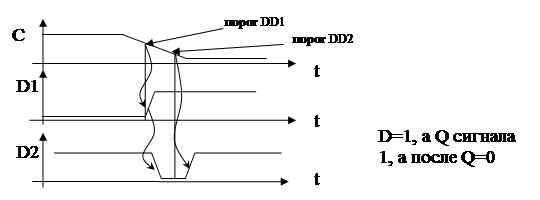

состояние что и на D входе. Получается из синхронного RS триггера при объединении через инвертор R и S входов. D – DATA – данные, иногда DELAY – задержка, т.к. сигнал завершается до С. При С=0 триггер находится в режиме хранения, т.е. изменения сигнала на D входе не влияет на Q выход триггера. При С=1 этот D триггер прозрачен для сигнала на D входе: этот сигнал сразу же появляется на Q выходе как только появится на D входе. Прозрачность триггера может привести к срабатыванию его от помех, как например, в предыдущем разделе, прозрачный RS триггер сработал от импульса помехи в конце диаграммы. Минимизированная для ТТЛ схема D триггера имеет некоторую склонность к ложным срабатываниям, если фронт сигнала на С входе 1-0 слишком пологий, а порог срабатывания D1 выше D2. такая ситуация называется гонками по входу. состояние что и на D входе. Получается из синхронного RS триггера при объединении через инвертор R и S входов. D – DATA – данные, иногда DELAY – задержка, т.к. сигнал завершается до С. При С=0 триггер находится в режиме хранения, т.е. изменения сигнала на D входе не влияет на Q выход триггера. При С=1 этот D триггер прозрачен для сигнала на D входе: этот сигнал сразу же появляется на Q выходе как только появится на D входе. Прозрачность триггера может привести к срабатыванию его от помех, как например, в предыдущем разделе, прозрачный RS триггер сработал от импульса помехи в конце диаграммы. Минимизированная для ТТЛ схема D триггера имеет некоторую склонность к ложным срабатываниям, если фронт сигнала на С входе 1-0 слишком пологий, а порог срабатывания D1 выше D2. такая ситуация называется гонками по входу.

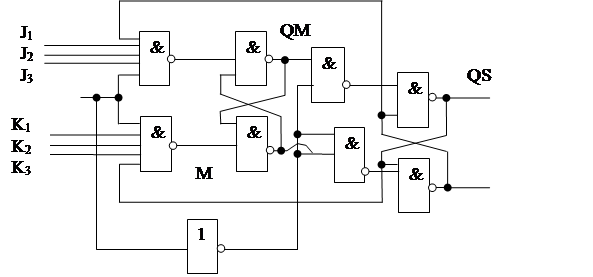

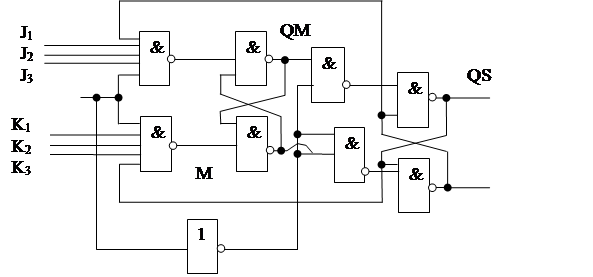

Синхронный двухступенчатый JK триггер.

1.При J=0 (какой-либо из J1, J2, или J3=0, J1*J2*J3=0) и К=0 (К1К2К3=0) сигнал лог 1 на С входе не может открыть входные ЛЭ, И-НЕ триггер не меняет связи состояния – режим хранения.

2.При J=1, К=0 первый RS триггер М переключается в 1 (QM=1) при поступлении на С вход лог 1 (фронт С01), а второй RS триггер S переключателей в 1 (QS=1) при фронт С10 [режим установка].

3. При J=0, K=1 QM→0 по С01, QS→0 по С10. [сброс]

4. При J=K=1 сигналы с выходов  открывают для С именно тот ЛЭ И-НЕ, пройдя через который он переключает триггер в противоположное положение в два этапа: сначала при С01 переключается QM, а затем по С10 – QS [счетный режим, или Т режим]. открывают для С именно тот ЛЭ И-НЕ, пройдя через который он переключает триггер в противоположное положение в два этапа: сначала при С01 переключается QM, а затем по С10 – QS [счетный режим, или Т режим].

Триггер непрозрачен, т.е. сигналы, поступающие на входы J и K не проходят сразу же на выход QS триггера, как это происходит в синхронных RS и D триггерах, рассмотренных ранее.

| C

| C

| J

| K

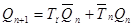

| Qn+1

| | x

| x

|

|

| Qn

|    ↓ ↓

|

|

|

|

| | ↓

|

|

|

|

|  ↓ ↓

|

|

|

| Qn

| В этом триггере видны параллельные пути распространения фронтов сигнала со входа С, которые являются причиной гонок. Чтобы микросхемы таких JK триггеров не давали сбоев, в них опасность гонок ликвидируется за счет или нормирования минимальной задержки М ступени, или специально введенный гарантированный разницы в порогах срабатывания инвертора и входных схем И ступени М. Делают так, чтобы инвертор переключался при более низком уровне С- сигнала, чем входные схемы 6И, и тогда нужная последовательность срабатывания инвертора и М ступени обеспечивается за счет конечной длительности фронтов С сигнала. Инвертор реагирует на фронт С01 сигнала раньше, а на его С10 позже, чем это делает М-ступень.

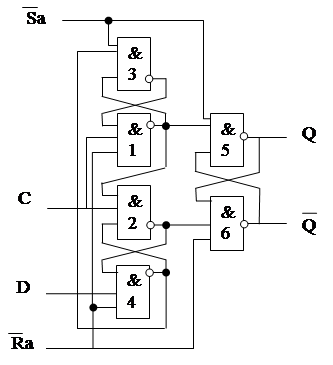

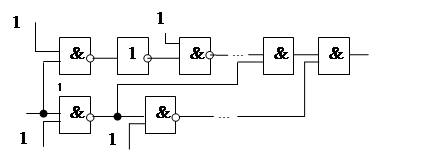

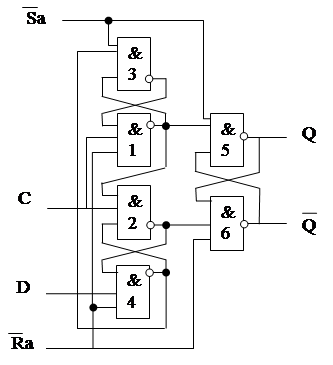

Шестиэлементный D триггер

Самый распространенный ТТЛ триггер. Другие его названия триггер Вебба, триггер с самоблокировкой, схема трех триггеров. Является непрозрачным. Переключение выхода Q триггера происходит по фронту С01. Схема противогоночная и допускает любые сочетания задержек своих элементов, т.к. в ней отсутствуют параллельные пути для гонок. Самый распространенный ТТЛ триггер. Другие его названия триггер Вебба, триггер с самоблокировкой, схема трех триггеров. Является непрозрачным. Переключение выхода Q триггера происходит по фронту С01. Схема противогоночная и допускает любые сочетания задержек своих элементов, т.к. в ней отсутствуют параллельные пути для гонок.

Назначение элементов:

5,6 – выходной RS триггер с инверсными входами

1,2 – входные схемы И-НЕ триггера RS

3,4 – вспомогательные И-НЕ, подготавливают одну из входных И-НЕ для открытия ее очередным фронтом С01.

Вначале пока С=0 триггер хранит предыдущее состояние, например Q=0. Изменение на D входе изменяют лишь состояния Л элементов 3 и 4, но не влияет на выходной RS триггер 5,6.

По первому фронту С01 открывается Л.Э.1 т.к. D=1 при этом и подключает выходной RS триггер в единичное состояние Q=1, т.е. происходит установка триггера.

По второму С01 фронту открывается Л.Э.2, т.к. D=0 при этом и триггер переключается в ноль. Q=0, т.е. сбрасывается триггер.

Изменение состояния на D входе поля С=1 не влияет на общее состояние триггера, так же как и при С=0. Следовательно, триггер переключается только фронтом С01.

|

На заводе изготовителе микросхем есть выходной контроль продукции, где отбраковывают НМС, у которых задержка распространения превышает допуск. Можно предположить, что микросхемы с задержкой, меньшей в 8 раз чем максимально допустимая, никогда не встретятся, но заводы изготовители такую гарантию не дают. Поэтому обычно считают, что задержка ЛЭ может быть от нуля до tзд.р. max и изготавливают это:

На заводе изготовителе микросхем есть выходной контроль продукции, где отбраковывают НМС, у которых задержка распространения превышает допуск. Можно предположить, что микросхемы с задержкой, меньшей в 8 раз чем максимально допустимая, никогда не встретятся, но заводы изготовители такую гарантию не дают. Поэтому обычно считают, что задержка ЛЭ может быть от нуля до tзд.р. max и изготавливают это:

0

0

Выход Q такого D триггера по сигналу на C входе принимает то же

Выход Q такого D триггера по сигналу на C входе принимает то же

состояние что и на D входе. Получается из синхронного RS триггера при объединении через инвертор R и S входов. D – DATA – данные, иногда DELAY – задержка, т.к. сигнал завершается до С. При С=0 триггер находится в режиме хранения, т.е. изменения сигнала на D входе не влияет на Q выход триггера. При С=1 этот D триггер прозрачен для сигнала на D входе: этот сигнал сразу же появляется на Q выходе как только появится на D входе. Прозрачность триггера может привести к срабатыванию его от помех, как например, в предыдущем разделе, прозрачный RS триггер сработал от импульса помехи в конце диаграммы. Минимизированная для ТТЛ схема D триггера имеет некоторую склонность к ложным срабатываниям, если фронт сигнала на С входе 1-0 слишком пологий, а порог срабатывания D1 выше D2. такая ситуация называется гонками по входу.

состояние что и на D входе. Получается из синхронного RS триггера при объединении через инвертор R и S входов. D – DATA – данные, иногда DELAY – задержка, т.к. сигнал завершается до С. При С=0 триггер находится в режиме хранения, т.е. изменения сигнала на D входе не влияет на Q выход триггера. При С=1 этот D триггер прозрачен для сигнала на D входе: этот сигнал сразу же появляется на Q выходе как только появится на D входе. Прозрачность триггера может привести к срабатыванию его от помех, как например, в предыдущем разделе, прозрачный RS триггер сработал от импульса помехи в конце диаграммы. Минимизированная для ТТЛ схема D триггера имеет некоторую склонность к ложным срабатываниям, если фронт сигнала на С входе 1-0 слишком пологий, а порог срабатывания D1 выше D2. такая ситуация называется гонками по входу.

открывают для С именно тот ЛЭ И-НЕ, пройдя через который он переключает триггер в противоположное положение в два этапа: сначала при С01 переключается QM, а затем по С10 – QS [счетный режим, или Т режим].

открывают для С именно тот ЛЭ И-НЕ, пройдя через который он переключает триггер в противоположное положение в два этапа: сначала при С01 переключается QM, а затем по С10 – QS [счетный режим, или Т режим].

↓

↓

↓

↓

Самый распространенный ТТЛ триггер. Другие его названия триггер Вебба, триггер с самоблокировкой, схема трех триггеров. Является непрозрачным. Переключение выхода Q триггера происходит по фронту С01. Схема противогоночная и допускает любые сочетания задержек своих элементов, т.к. в ней отсутствуют параллельные пути для гонок.

Самый распространенный ТТЛ триггер. Другие его названия триггер Вебба, триггер с самоблокировкой, схема трех триггеров. Является непрозрачным. Переключение выхода Q триггера происходит по фронту С01. Схема противогоночная и допускает любые сочетания задержек своих элементов, т.к. в ней отсутствуют параллельные пути для гонок.