- Автоматизация

- Антропология

- Археология

- Архитектура

- Биология

- Ботаника

- Бухгалтерия

- Военная наука

- Генетика

- География

- Геология

- Демография

- Деревообработка

- Журналистика

- Зоология

- Изобретательство

- Информатика

- Искусство

- История

- Кинематография

- Компьютеризация

- Косметика

- Кулинария

- Культура

- Лексикология

- Лингвистика

- Литература

- Логика

- Маркетинг

- Математика

- Материаловедение

- Медицина

- Менеджмент

- Металлургия

- Метрология

- Механика

- Музыка

- Науковедение

- Образование

- Охрана Труда

- Педагогика

- Полиграфия

- Политология

- Право

- Предпринимательство

- Приборостроение

- Программирование

- Производство

- Промышленность

- Психология

- Радиосвязь

- Религия

- Риторика

- Социология

- Спорт

- Стандартизация

- Статистика

- Строительство

- Технологии

- Торговля

- Транспорт

- Фармакология

- Физика

- Физиология

- Философия

- Финансы

- Химия

- Хозяйство

- Черчение

- Экология

- Экономика

- Электроника

- Электротехника

- Энергетика

Таблица 7.12

Таблица 7.12

| № импульса | Q

| Q

| Q

| Q

|

8

| ||||

При построении счетчиков, использующих систему счисления, отличную от двоичной, используются обратные связи. Широкое применение нашли счетчики, фиксирующие каждый десятый импульс. В их состав входят четыре Т-триггера, соединенных по схеме рис. 7.22,а. Состояние такого счетчика до седьмого импульса не отличается от состояния суммирующего счетчика, показанного в табл. 7.10. После прохождения восьмого импульса вначале первые три триггера переходят в состояние “0”, а четвертый в состояние “1”. Однако по цепи обратной связи логическая “1” с выхода четвертого триггера подается на установочные входы S второго и третьего триггеров, после чего их состояния становятся “1”. Этот переход отражен в табл. 7.12 двумя строками – 8  и 8. После прохождения девятого импульса все триггеры переходят в состояние “1”, а после десятого – в состояние “0”. Включением в состав счетчика четырехвходового логического элемента “И-НЕ”, на вход которого подается информация с выходов триггеров, достигается появление на выходе счетчика “1” после прохождения каждого десятого импульса. Схемное обозначение такого счетчика приведено на рис. 7.26,б.

и 8. После прохождения девятого импульса все триггеры переходят в состояние “1”, а после десятого – в состояние “0”. Включением в состав счетчика четырехвходового логического элемента “И-НЕ”, на вход которого подается информация с выходов триггеров, достигается появление на выходе счетчика “1” после прохождения каждого десятого импульса. Схемное обозначение такого счетчика приведено на рис. 7.26,б.

7.7. Регистры

Регистрами называют устройства, предназначенные для приема, хранения и передачи информации, представленной в виде двоичного числа. В отличие от триггеров эти операции производятся с информацией, содержащей n-разрядов. Регистры строятся с использованием синхронных D-триггеров, число которых определяется разрядом числа, подлежащего хранению. В зависимости от характера ввода информации различают параллельные и последовательные регистры.

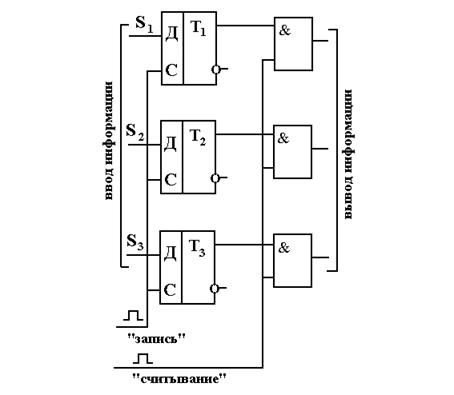

Рисунок 7.27. Схема параллельного регистра

В параллельном регистре информация поступает на все n триггеров одновременно по параллельным n каналам, как показано на рис. 7.27 для n = 3. Ее ввод в регистр осуществляется подачей тактового импульса на объединенный синхронный вход С. Регистр запоминает информацию, поскольку каждый его триггер переходит в состояние, соответствующее той информации, которая была на входе триггера в момент подачи тактового импульса. Отсутствие логической “1” на синхронном входе защищает регистр от попадания в него ложной информации. На выходе каждого D-триггера включают двухвходовые элементы “И”, на вторые входы которых подается импульс при съеме информации и передаче ее по n параллельным каналам.

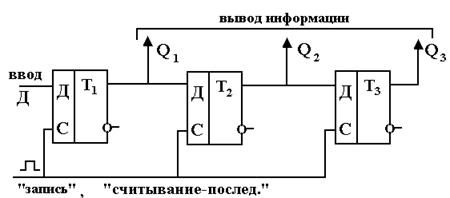

Рисунок 7.28. Схема последовательного регистра

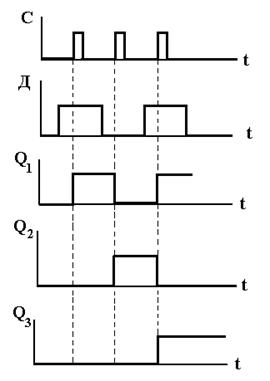

Рисунок 7.29. Временные диаграммы, иллюстрирующие

работу последовательного регистра

В последовательном регистре D-триггеры включены последовательно, как показано на рис. 7.28 для n = 3. Регистр имеет один вход D, на который подается информация по одному каналу в виде последовательного кода, т.е. в виде разнесенных во времени логических “1” и “0”, начиная со старшего разряда, как показано на временной диаграмме рис. 7.29. Ввод информации в регистр осуществляется подачей на объединенный синхронный вход триггеров ряда тактовых импульсов, число которых равно разряду числа, подлежащего вводу в регистр. Причем в момент подачи i-го тактового импульса на входе D-триггера должна быть информация, соответствующая (n + 1 – i) – му разряду числа. Таким образом, с подачей последовательности тактовых импульсов вводимая информация постоянно “сдвигается” по цепочке триггеров и после окончания последнего, n-го импульса триггеры будут находиться в таких состояниях, что состояние входного триггера будет соответствовать первому разряду числа, а последнего – старшему разряду. В связи с такой последовательностью введения информации последовательные регистры часто называют регистрами сдвига. Временные диаграммы рис. 7.29 показывают введение в такой регистр числа 101.

Съем информации с последовательного регистра может быть осуществлен как в виде последовательного кода, так и в виде параллельного (на один канал или n каналов). На параллельные каналы съем производится с выходов Q каждого триггера. С этой целью должен подаваться один тактируемый импульс на входы логических элементов “И”, устанавливаемых на выходах Q триггеров, как и в схеме рис. 7.27. Съем информации в виде последовательного кода производится с выхода Q выходного триггера. Для ее передачи в канал на объединенный синхронный вход триггеров подается n тактируемых импульсов, в результате чего информация такт за тактом сдвигается в направлении к выходу регистра. При этом информация в регистре не сохраняется. Следует отметить, что последовательный регистр, кроме хранения информации, позволяет ее преобразовывать из последовательного кода в параллельный.

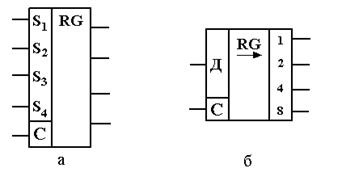

Рисунок 7.30. Схемное обозначение регистров:

а - параллельного, б - последовательного

На рис. 7.30 представлены схемные обозначения параллельного и последовательного регистров.

|

|

|

© helpiks.su При использовании или копировании материалов прямая ссылка на сайт обязательна.

|